1/6ページ

ダウンロード

【技術記事】画期的かつスケーラブルなパワー・シーケンス・システム、多くの電源レールを対象とする設計/デバッグを大幅に簡素化

ホワイトペーパー

著者: Navdeep Singh Dhanjal Analog Devices, Inc.

はじめに

周知のとおり、あらゆる分野の電子システムは、ますます複雑になっています。しかし、その複雑さが電源の設計にまで及んでいることは、それほど認識されていません。例えば、機能的な複雑さに対応するために、ASIC、FPGA、マイクロプロセッサを使用して、アプリケーションの豊富な機能セットをより小さなフォーム・ファクタに詰め込むというのはよく行われていることです。それらのデジタル・デバイスは、電源システムにとっての新たな負荷になります。

電圧値の異なる電源レールがいくつも必要になり、各レールの許容範囲もそれぞれ全く異なります。また、正しいシーケンスで電源を投入/遮断することも、非常に重要な要件となります。基板上に複数の電源レールが配置されると、電源の投入/遮断シーケンスの設計とデバッグの複雑さは、指数関数的に増大します。

◆続きはカタログをダウンロードしてご覧下さい。

このカタログについて

| ドキュメント名 | 【技術記事】画期的かつスケーラブルなパワー・シーケンス・システム、多くの電源レールを対象とする設計/デバッグを大幅に簡素化 |

|---|---|

| ドキュメント種別 | ホワイトペーパー |

| 取り扱い企業 | アナログ・デバイセズ株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

デザイン・ノート

Share on Twitter Facebook LinkedIn Email

画期的かつスケーラブルなパワー・

シーケンス・システム、多くの電源レールを

対象とする設計/デバッグを大幅に簡素化

著者: Navdeep Singh Dhanjal

Analog Devices, Inc.

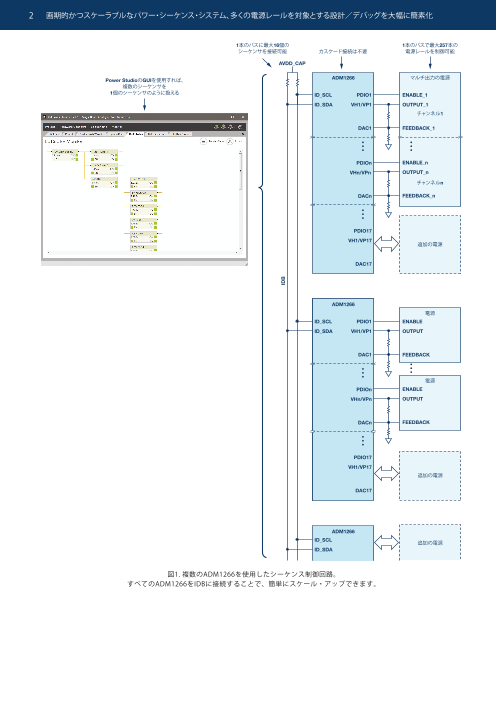

はじめに 「ADM1266」は、アナログ・デバイセズのSuper Sequencer®

周 知 の と お り 、 あ ら ゆ る 分 野 の 電 子 シ ス テ ム は 、 ま す ま

ファミリに新たに加わった製品です。この製品を採用すれば、

す複雑に 真のスケーラビリティによって、複雑さの問題を解決すること

なっています。しかし、その複雑さが電源の設計にまで及んでい ができます。複数のADM1266を接続する場合、専用の2線式デ

ることは、それほど認識されていません。例えば、機能的な複雑 バイス間バス(IDB:Interdevice Bus)を使用して通信を行い

さに対応するために、ASIC、FPGA、マイクロプロセッサを使用して、 ます。1個のADM1266で、17本の電源レールの監視とシーケン

アプリケーションの豊富な機能セットをより小さなフォーム・ファク ス制御が可能です。同ICは、最大で16個並列に接続できます。

タに詰め込むというのはよく行われていることです。それらのデジ すべてを同一のIDBに接続すれば、257本の電源レールの監視/

タル・デバイスは、電源システムにとっての新たな負荷になります。 シーケンス制御を実現可能です。

電圧値の異なる電源レールがいくつも必要になり、各レールの許

容範囲もそれぞれ全く異なります。また、正しいシーケンスで電 ADM1266は、シングル・マスタ方式を採用しています。マスタ

源を投入/遮断することも、非常に重要な要件となります。基板 以外のADM1266は、すべてスレーブとして動作します。その並

上に複数の電源レールが配置されると、電源の投入/遮断シーケ 列アーキテクチャにより、IDBに接続されたすべてのADM1266

ンスの設計とデバッグの複雑さは、指数関数的に増大します。 は、システムの条件に基づいて同一の状態に遷移します。それ

によって、バス上のすべてのADM1266の同期が確保されます。

スケーラビリティ バスによる通信はトランスペアレントなものであり、ADM1266

が1個の場合でも16個の場合でも、シーケンスを作成する作業

アプリケーションで使用する基板に必要な電源レールの数は、 は同じです。このシステムがもたらす顕著なメリットは、1個の

基板の複雑さに依存します。電源レールは10本しか必要ないこ デバイスの使用方法を習得するだけで、単純な設計と複雑な設

ともあれば、200本も必要になるケースもあります。通常のシ 計の両方に対応できることです。言い換えれば、それぞれのケ

ーケンサICは約16本までの電源レールに対応し、その本数まで ースに応じて異なるデバイスの使用方法を習得する必要はあり

なら簡単に適用できるように設計されています。電源レールの ません。図1に示すように、同じIDBに接続するだけで、複数の

数が1個のシーケンサで対応できる本数を超えると、複雑さは急 ADM1266を簡単にカスケード接続することができます。

激に増大します。その結果、設計者は、各シーケンサの予測不

能な挙動や、複雑なシステムにシーケンサを組み込む方法につ イベント・ベースのシーケンス制御

いて学ばなければならなくなります。 最新のシーケンサは、電源レールを監視するだけでなく、デジ

多数の電源レールを使用するシステムでは、複数のシーケンサ タル信号にも対応する必要があります。従来の時間ベースのシ

をカスケード接続することで対応を図ることはよくあります。 ーケンサには、特定の結果に対応づけられた固定の信号だけが

ただ、そのために必要になる作業は、それほど単純なものでは 用意されており、機能も限定されていました。

ありません。電源レールの本数が線形的に増加すると、カスケ

ード接続のシステムの複雑さは、指数関数的に増大します。そ ここで、オプションのドーター・ボードを接続したマザーボー

うした複雑さを抑えるために、シーケンサをカスケード接続す ドの例を考えてみます。ドーター・カードの検出信号は、シー

るための方法には、独創的な工夫が盛り込まれています。例え ケンサで監視されます。信号が存在する場合、シーケンサはド

ば、ピンポン機構を利用したり、専用のデジタル信号によって ーター・カード上の電源レールを起動します。信号が存在しな

フォルトとパワー・グッドの状態を共有したり、といった具合 い場合には、マザーボードのシーケンス処理をパワー・グッド

です。そうしたソリューションは、比較的単純明快なシーケン の状態になるまで続行します。このドーター・カードの検出信

スに対しては、十分な効果をもたらします。しかし、電源の投 号のような仕組みは、従来型のほとんどのシーケンサでは利用

入/停止のシーケンスが単純ではないシステムでは、それらの できません。また、この種の要件はアプリケーションごとに異

ソリューションではすぐに歯が立たなくなります。 なり、GPIO(General Purpose Inputs Outputs)によって処理する必要があります。

analog.com/jp

Page2

2 画期的かつスケーラブルなパワー・シーケンス・システム、多くの電源レールを対象とする設計/デバッグを大幅に簡素化

1本のバスに最大16個の 1本のバスで最大257本の

シーケンサを接続可能 カスケード接続は不要 電源レールを制御可能

AVDD_CAP

Power StudioのGUIを使用すれば、 ADM1266 マルチ出力の電源

複数のシーケンサを

1個のシーケンサのように扱える ID_SCL PDIO1 ENABLE_1

ID_SDA VH1/VP1 OUTPUT_1

チャンネル1

DAC1 FEEDBACK_1

• •

•

PDIOn ENABLE_n

VHn/VPn OUTPUT_n

チャンネルn

DACn FEEDBACK_n

••

•

PDIO17

VH1/VP17

追加の電源

DAC17

ADM1266

電源

ID_SCL PDIO1 ENABLE

ID_SDA VH1/VP1 OUTPUT

DAC1 FEEDBACK

•

••

電源

PDIOn ENABLE

VHn/VPn OUTPUT

DACn FEEDBACK

•

••

PDIO17

VH1/VP17

追加の電源

DAC17

ADM1266

ID_SCL 追加の電源

ID_SDA

図1. 複数のADM1266を使用したシーケンス制御回路。

すべてのADM1266をIDBに接続することで、簡単にスケール・アップできます。

IDB

• • • • • •

Page3

3 画期的かつスケーラブルなパワー・シーケンス・システム、多くの電源レールを対象とする設計/デバッグを大幅に簡素化

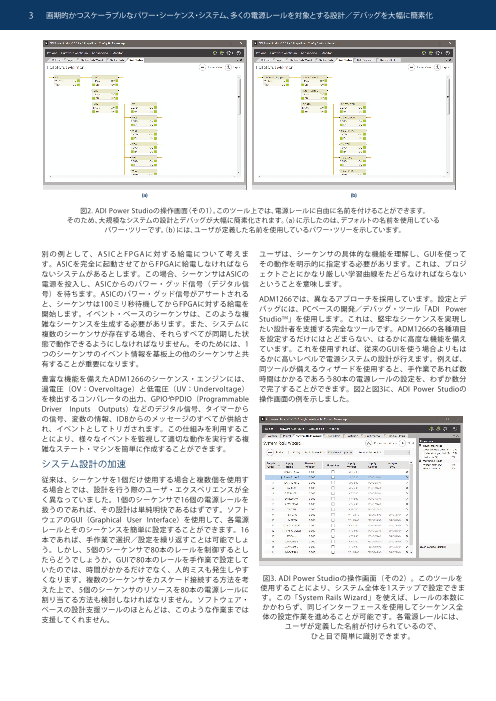

(a) (b)

図2. ADI Power Studioの操作画面(その1)。このツール上では、電源レールに自由に名前を付けることができます。

そのため、大規模なシステムの設計とデバッグが大幅に簡素化されます。(a)に示したのは、デフォルトの名前を使用している

パワー・ツリーです。(b)には、ユーザが定義した名前を使用しているパワー・ツリーを示しています。

別 の 例 と し て 、 A S I C と F P G A に 対 す る 給 電 に つ い て 考 え ま ユーザは、シーケンサの具体的な機能を理解し、GUIを使って

す。ASICを完全に起動させてからFPGAに給電しなければなら その動作を明示的に指定する必要があります。これは、プロジ

ないシステムがあるとします。この場合、シーケンサはASICの ェクトごとにかなり厳しい学習曲線をたどらなければならない

電源を投入し、ASICからのパワー・グッド信号(デジタル信 ということを意味します。

号)を待ちます。ASICのパワー・グッド信号がアサートされる

と、シーケンサは100ミリ秒待機してからFPGAに対する給電を ADM1266では、異なるアプローチを採用しています。設定とデ

開始します。イベント・ベースのシーケンサは、このような複 バッグには、PCベースの開発/デバッグ・ツール「ADI Power

雑なシーケンスを生成する必要があります。また、システムに Studio

TM」を使用します。これは、堅牢なシーケンスを実現し

複数のシーケンサが存在する場合、それらすべてが同期した状 たい設計者を支援する完全なツールです。ADM1266の各種項目

態で動作できるようにしなければなりません。そのためには、1 を設定するだけにはとどまらない、はるかに高度な機能を備え

つのシーケンサのイベント情報を基板上の他のシーケンサと共 ています。これを使用すれば、従来のGUIを使う場合よりもは

有することが重要になります。 るかに高いレベルで電源システムの設計が行えます。例えば、同ツールが備えるウィザードを使用すると、手作業であれば数

豊富な機能を備えたADM1266のシーケンス・エンジンには、 時間はかかるであろう80本の電源レールの設定を、わずか数分

過電圧(OV:Overvoltage)と低電圧(UV:Undervoltage) で完了することができます。図2と図3に、ADI Power Studioの

を検出するコンパレータの出力、GPIOやPDIO(Programmable 操作画面の例を示しました。

Driver Inputs Outputs)などのデジタル信号、タイマーから

の信号、変数の情報、IDBからのメッセージのすべてが供給さ

れ、イベントとしてトリガされます。この仕組みを利用するこ

とにより、様々なイベントを監視して適切な動作を実行する複

雑なステート・マシンを簡単に作成することができます。

システム設計の加速

従来は、シーケンサを1個だけ使用する場合と複数個を使用す

る場合とでは、設計を行う際のユーザ・エクスペリエンスが全

く異なっていました。1個のシーケンサで16個の電源レールを

扱うのであれば、その設計は単純明快であるはずです。ソフト

ウェアのGUI(Graphical User Interface)を使用して、各電源

レールとそのシーケンスを簡単に設定することができます。16

本であれば、手作業で選択/設定を繰り返すことは可能でしょ

う。しかし、5個のシーケンサで80本のレールを制御するとし

たらどうでしょうか。GUIで80本のレールを手作業で設定して

いたのでは、時間がかかるだけでなく、人的ミスも発生しやす

くなります。複数のシーケンサをカスケード接続する方法を考 図3. ADI Power Studioの操作画面(その2)。このツールを

えた上で、5個のシーケンサのリソースを80本の電源レールに 使用することにより、システム全体を1ステップで設定できま

割り当てる方法も検討しなければなりません。ソフトウェア・ す。この「System Rails Wizard」を使えば、レールの本数に

ベースの設計支援ツールのほとんどは、このような作業までは かかわらず、同じインターフェースを使用してシーケンス全

支援してくれません。 体の設定作業を進めることが可能です。各電源レールには、

ユーザが定義した名前が付けられているので、

ひと目で簡単に識別できます。

Page4

4 画期的かつスケーラブルなパワー・シーケンス・システム、多くの電源レールを対象とする設計/デバッグを大幅に簡素化

シーケンスの設定は、一般的には次のような手順で実施しま 不具合の多くは、信号のロジック・レベルが誤っていることで

す。設計者は、まずシステムの要件を満たす仮想ステート・マ 発生します。それだけでなく、電源レールの起動/停止が適切

シンを作成します。シーケンサが1個(レール数が17本以下) でないことに起因する不具合も数多く発生します。

の場合、GUI上の仮想ステート・マシンは、シーケンサのステ

ート・マシンと完全に一致します。シーケンサが複数になる ここで、80本の電源レールを備える基板に電源を投入するケー

と、仮想ステート・マシンと、個々のシーケンサのステート・ スを考えます。設計の段階で、どれか1本のレールが正しく設定

マシンに違いが出てきます。複数のシーケンサが様々なイベン されていなかったというのは、珍しいことではありません。コ

トを互いにやり取りするので、ステート・マシンには追加のス ンポーネントのレベルや設定のレベルで誤りがあるために不具

テップが必要になるのです。 合が生じるのはよくあることです。いずれにせよ、まずは不具合が発生している電源レールを特定する必要があります。ここ

例として、シーケンサ1で2本の電源レールを監視し、シーケン で問題になるのは、一般的なシーケンスでは、いずれかの電源

サ2で別の2本の電源レールを監視するケースを考えます。4本 レールに異常が発生したら、シーケンサによってすべての電源

の電源レールのうちいずれかに障害が発生した場合、すべての レールがシャットダウンされることです。この動作は、システ

レールをシャットダウンする必要があります。そのためには、2 ムが実際に稼働する際の堅牢性を保証するためには欠かせない

個のシーケンサの間でフォルト信号を共有しなければなりませ ものです。しかし、設計の段階では、この動作がデバッグの妨

ん。図4に、システムの仮想ステート・マシンと、個々のシーケ げになります。システム全体が異常終了し、どこに不具合があ

ンサのステート・マシンを示しました。 るのかがわからなくなるのです。設計者は、いわば森が邪魔で

木を見ることができない状態になります。80本すべてのレール

仮想ステート・マシン を同時にベンチトップ型の計測器でモニタリングするのは現実

もし (シーケンサ1のレール1 または

シーケンサ1のレール2 または

シーケンサ2のレール1 または 的ではなく、不具合が発生しているレールの特定は非常に困難

シーケンサ2のレール2がフォルト)

である場合には、すべてをディスエーブルにする になります。

シーケンサ1のステート・マシン

もし (シーケンサ1のレール1 または 不具合のある電圧レールが検出されても他の電圧レールはその

シーケンサ1のレール2 または

フォルト信号がフォルト) まま起動しておき、それらに対応する部分を稼働させながら、

である場合には、すべてをディスエーブルにする 問題のレールの動作を観測することができれば、デバッグ用の

シーケンサ2のステート・マシン

もし (シーケンサ2のレール1 または システムとして理想的です。シーケンスの設定を強制的に変更

シーケンサ2のレール2 または

フォルト信号がフォルト) することでも同じことを実現できますが、シーケンスのデバッ

である場合には、すべてをディスエーブルにする

グを行うために、わざわざシーケンスの設定を不適切な方向に

変更するのは面倒だと言わざるを得ません。

図4. 仮想ステート・マシンと

各シーケンサのステート・マシン ADI Power StudioとADM1266を組み合わせた場合、デバッグ作業を簡素化するためにソフトウェア設計環境で一般的に使わ

電源レールの数が増え、シーケンスの要件が複雑になるにつれ れる高度なデバッグ・ツールを使用できます。1つ目のデバッ

て、システムの仮想ステート・マシンとシーケンサのステー グ・ツールはブレークポイントです。ブレークポイントを使

ト・マシンの違いは大きくなっていきます。どのような状態に えば、シーケンスの進行を特定の状態で停止させることができ

なればよいのか把握していたとしても、その状態になるように ます。複数のADM1266を使用するシステムの場合、すべての

複数のシーケンサを連動させるのは容易ではありません。時間 ADM1266がステート・マシンに従って遷移し、ユーザが設定し

がかかるだけでなく、バグが入り込みやすい作業になるからで たブレークポイントの手前で停止します。このようにしてシー

す。 ケンスを一時停止させることにより、正しく動作していない電源レールを見出したり、信号が正しいロジック・レベルになっ

ADI Power Studioは、ステート・マシンを作成する作業の多く ていない理由を検証したりすることができます(図5)。

を自動化します。GUIを使って仮想ステート・マシンを設計す

る作業は、ユーザが実施しなければなりません。しかし、複数

のシーケンサの間の複雑な通信は、ADI Power Studioのコンパ

イラが処理します。そのため、設計者は柔軟性が高く直感的に

理解できるプロセスによって、複雑なステート・マシンを実現

することができます。

強力なデバッグ・ツール

複雑なシステムを開発する場合、開発過程のあらゆる段階でバ

グが作り込まれる可能性があります。開発のどこかの段階で、

ほとんどのバグが検出されて取り除かれればよいのですが、な

かにはシステムの稼働時まで発見されずにいるバグも存在しま

す。したがって、システム設計者にとっては、不具合を素早く

特定し、それに対処するための修正を加えることのできるツー

ルが不可欠です。一般に、設計者は純粋な設計作業よりも、デ

バッグ作業にはるかに多くの時間を費やしているからです。

図5. ブレークポイントの設定。

シーケンスを任意の状態で一時停止することで、

詳細なデバッグを行うことができます。

Page5

5 画期的かつスケーラブルなパワー・シーケンス・システム、多くの電源レールを対象とする設計/デバッグを大幅に簡素化

また、すべての状態に対してブレークポイントを設定すれば、1

ステップずつシーケンスを実行することも可能です。このステ

ップ実行は、例えばイネーブルになる前の電源レールのプリバ

イアス起動を確認する場合に適用できます。また、電源シーケ

ンスのステップ実行によって、ディスエーブルであるはずのレ

ールの出力に電圧が生じていないかどうかということを、ADI

Power Studioのモニタ・ウィンドウのセクションを使って確認

することも可能です。

2つ目のデバッグ・ツールは、ブラックボックス記録機能で

す。ADM1266は、クリティカルなイベントによってトリガさ

れた際、監視したすべての電圧とデジタル・ピンの状態のスナ

ップショットを記録します。ブラックボックスがトリガされる

と、イベントが発生したときの状態、それ以前の良好な状態、

イベントが発生した時間、ADM1266が起動した回数、障害が発

生した回数などの情報が記録されます(図6)。これらの情報

は、障害が発生した個所を特定し、原因を迅速に診断する上で 図6. ブラックボックス記録機能の表示画面。ユーザが定義し

役に立ちます。 たイベントが発生した際の各種の状態が記録されています。

ブラックボックス記録機能は、システムが運用された際、障害 実際に配備するシステムに、この機能に対するトリガを

の状況を捉える上で重要な役割を担います。システムのメンテ 含めれば、フィールドでのトラブルシューティング、

ナンスとアップグレードに役立つ機能ですが、これを開発時の メンテナンス、デバッグが容易になります。

デバッグ・ツールとして利用することもできます。例えば、サ

ーマル・チャンバを使用したテストや機械的なテストを実施す まとめ

る際など、ベンチトップ型計測器のプローブを使用するのは不 ますます複雑さを増す電源の投入/遮断シーケンスの要件に対

可能なケースがあります。そのような場合に、ブラックボック 応するには、スケーラブルかつ機能が豊富で、直感的に使用で

ス記録機能を使用すれば、障害の発生を捉えて後で確認するこ きるソリューションが必要です。ADI Power Studioと17チャン

とができます。 ネルに対応するシーケンサであるADM1266を採用すれば、高

度な設計/デバッグ・ツールを使用することにより、開発時間

とデバッグ時間を短縮することができます。その結果、設計者

は、イノベーションの創出と堅牢なソリューションの構築に、

より多くの時間を費やすことが可能になります。

Page6

著者について オンライン・

Navdeep Singh Dhanjal(navdeep.dhanjal@analog. サポート・

com)は、アナログ・デバイセズで14年間にわたりデジ コミュニティ

タル電源やSuper Sequencer®などの画期的な製品に携わ アナログ・デバイセズのオンライン・サポート・コミュ

ってきました。直感的に操作が可能なデジタル電源製品

向けのGUIを設計した経験を持ちます。最近では、Super ニティに参加すれば、各種の分野を専門とする技術者

Sequencer製品「ADM1266」の設計者として、ファーム との連携を図ることができます。難易度の高い設計上

ウェア、ソフトウェア、ハードウェアの開発を統括しま の問題について問い合わせを行ったり、FAQ を参照し

した。サンノゼ州立大学で電気工学の修士号を取得。3 たり、ディスカッションに参加したりすることが可能

件の特許を保有しています。 です。

ez.analog.com にアクセス

*英語版デザイン・ノートはこちらよりご覧いただけます。

本 社 〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル10F

大阪営業所 〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪トラストタワー10F

名古屋営業所 〒451-6040 愛知県名古屋市西区牛島町6-1 名古屋ルーセントタワー38F

©2019 Analog Devices, Inc. All rights reserved.

本紙記載の商標および登録商標は、

各社の所有に属します。

Ahead of What’s Possible は

アナログ・デバイセズの商標です。 www.analog.com/jp

DN21154-0-2/19