1/12ページ

ダウンロード(8.8Mb)

このホワイトペーパーでは、⻑期間保管された表⾯実装技術(SMT)製品から、様々な保管期間の製品を選択し、 はんだ付け性と基板実装性能を評価しています。

デートコードによる制限には根拠がないことが業界で認識されつつありますが、半導体製品を

使⽤している顧客や製造委託業者のなかには、購⼊する製品のデートコードを指定して、デー

トコードの古い製品に対し制限を課している場合もあります。

今回の検証は、半導体市場に属する企業が実施した検証や、ロチェスターエレクトロニクスに

おいて実施した検証の結果、⻑期保管による劣化の証拠が⾒つからなかったことを踏まえ、そ

の検証範囲を拡⼤させたものとなっています。

ここでは、⻑期間保管された表⾯実装技術(SMT)製品から、様々な保管期間の製品を選択し、

はんだ付け性と基板実装性能を評価しています。” ディップ&ルック(はんだ槽/浸漬および外

観試験)” および” SMTシミュレーション(表⾯実装プロセスシミュレーション試験)” の両⽅の

はんだ付け性試験⽅法では、製品の保管年数とは相関しない不具合が発⽣し、プリント回路基

板(PCB)の組⽴でも再現はされませんでした。

このPCB実装⼯程は実際の使⽤条件に最も近いため、デートコードに基づく制限や追加要件を

裏付ける証拠はないと結論付けました。

内容一例:

・IPC/JEDEC J-STD-002 はんだ付け性試験

・プリント基板への実装

・部品実装後の断面検査と電子顕微鏡検査

・電気的試験

など

詳しくはぜひ資料をダウンロードしてご確認ください!

このカタログについて

| ドキュメント名 | 【ホワイトペーパー】半導体製品の長期保管に対するはんだ付け性試験の適合性 |

|---|---|

| ドキュメント種別 | ホワイトペーパー |

| ファイルサイズ | 8.8Mb |

| 取り扱い企業 | Rochester Electronics,Ltd. (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

A Rochester Electronics White Paper

半導体製品の⻑期保管に対する

はんだ付け性試験の適合性

Rochester Electronics, Ltd. ⽇本営業本部

170-6011 東京都豊島区東池袋 3-1-1 サンシャイン 60 ビル 11 階

+81.3.4579.0834 / www.rocelec. jp

Page2

概要

デートコードによる制限には根拠がないことが業界で認識されつつありますが、半導体製品を

使⽤している顧客や製造委託業者のなかには、購⼊する製品のデートコードを指定して、デー

トコードの古い製品に対し制限を課している場合もあります。

今回の検証は、半導体市場に属する企業が実施した検証や、ロチェスターエレクトロニクスに

おいて実施した検証の結果、⻑期保管による劣化の証拠が⾒つからなかったことを踏まえ、そ

の検証範囲を拡⼤させたものとなっています。

ここでは、⻑期間保管された表⾯実装技術(SMT)製品から、様々な保管期間の製品を選択し、

はんだ付け性と基板実装性能を評価しています。” ディップ&ルック(はんだ槽/浸漬および外

観試験)” および” SMT シミュレーション(表⾯実装プロセスシミュレーション試験)” の両⽅の

はんだ付け性試験⽅法では、製品の保管年数とは相関しない不具合が発⽣し、プリント回路基

板(PCB)の組⽴でも再現はされませんでした。

この PCB 実装⼯程は実際の使⽤条件に最も近いため、デートコードに基づく制限や追加要件を

裏付ける証拠はないと結論付けました。

⽬次

概要 ........................................................................................................................................................................... 2

1. はじめに ............................................................................................................................................................ 3

2. サンプル ............................................................................................................................................................ 3

3.⼿順 ..................................................................................................................................................................... 4

4.IPC/JEDEC J-STD-002 はんだ付け性試験 .................................................................................................... 5

4.1.ディップ&ルック試験 .......................................................................................................................... 5

4.2.SMT シミュレーション試験 ................................................................................................................. 5

4.3.リード前処理⽅法(ベーキング式前処理と上記式加湿処理の⽐較) ................................................. 7

4.4 繰返し性と再現性 ................................................................................................................................... 8

5.プリント基板への実装 ...................................................................................................................................... 9

6.部品実装後の断⾯検査と電⼦顕微鏡検査 ..................................................................................................... 10

7.電気的試験 ....................................................................................................................................................... 10

8.まとめ ............................................................................................................................................................... 11

参考情報 ................................................................................................................................................. 12

© Rochester Electronic, Ltd.

2

Page3

1.はじめに

ロチェスターエレクトロニクスが以前発表したホワイトペーパー[1]、[2]では、幅広い種類

の半導体製品が⻑期保管後も使⽤に適していることを実証しました。今回このホワイトペー

パーでは、経年劣化した表⾯実装製品のはんだ付け性試験の結果と PCB 組⽴性能を⽐較し

ています。その⽬的は、経年劣化した製品の端⼦が PCB パッドに⼀貫して密着しているか

どうか、またどの試験⽅法が基板実装の成功を最も効果的に予測できるかを理解することで

す。

半導体製品が使⽤可能かをスクリーニングするために、EIA/IPC/JEDEC共同規格 J-STD-

002[3]、または国防兵站庁規格MIL-STD-883[4]のいずれかに準拠したロボットはんだ槽浸

漬試験が、⼀般的に採⽤されています。この試験⽅法は、製造直後の製品を試験するために

設計されているため、経年劣化の影響をシミュレーションするための”前処理”ステップ(最

も⼀般的なものは⽔蒸気による前処理)が含まれています。

J-STD-002[3]の最新改訂版には、「プリント基板への物理的な製品取り付けは、はんだ付

け性検査操作の⼀部として [別のはんだ付け性試験⽅法] の代わりに使⽤できる」という許

可が⽰されています。本検証では、物理的製品実装のアプローチを採⽤し、⻑期保管後の製

品を試験する際に、他のはんだ付け性試験⽅法とは⼤きく異なる結果が得られることを発⾒

しました。

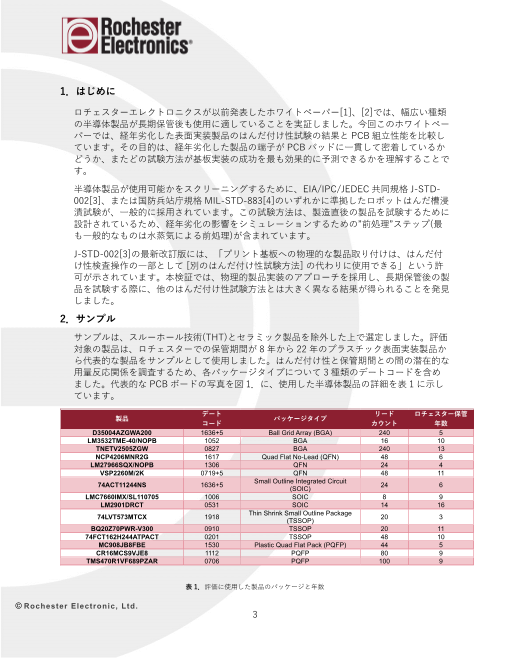

2.サンプル

サンプルは、スルーホール技術(THT)とセラミック製品を除外した上で選定しました。評価

対象の製品は、ロチェスターでの保管期間が 8年から 22 年のプラスチック表⾯実装製品か

ら代表的な製品をサンプルとして使⽤しました。はんだ付け性と保管期間との間の潜在的な

⽤量反応関係を調査するため、各パッケージタイプについて 3 種類のデートコードを含め

ました。代表的な PCBボードの写真を図 1.に、使⽤した半導体製品の詳細を表 1 に⽰し

ています。

製品 デート ロ

コード パッケージタイプ リード チェスター保管

カウント 年数

D35004AZGWA200 1636+5 Ball Grid Array (BGA) 240 5

LM3532TME-40/NOPB 1052 BGA 16 10

TNETV2505ZGW 0827 BGA 240 13

NCP4206MNR2G 1617 Quad Flat No-Lead (QFN) 48 6

LM27966SQX/NOPB 1306 QFN 24 4

VSP2260M/2K 0719+5 QFN 48 11

74ACT11244NS 1636+5 Small Outline Integrated Circuit

(SOIC) 24 6

LMC7660IMX/SL110705 1006 SOIC 8 9

LM2901DRCT 0531 SOIC 14 16

74LVT573MTCX 1918 Thin Shrink Small Outline Package

(TSSOP) 20 3

BQ20Z70PWR-V300 0910 TSSOP 20 11

74FCT162H244ATPACT 0201 TSSOP 48 10

MC908JB8FBE 1530 Plastic Quad Flat Pack (PQFP) 44 5

CR16MCS9VJE8 1112 PQFP 80 9

TMS470R1VF689PZAR 0706 PQFP 100 9

表 1.評価に使⽤した製品のパッケージと年数

© Rochester Electronic, Ltd.

3

Page4

図 1.PCB に実装された評価対象製品

3.⼿順

最終⽤途への製品の適合性を評価するために、さまざまな試験を実施しました。はんだ付け

性試験は、ディップ&ルック(J-STD-002 の試験 Aおよび A1)と SMT シミュレーション(試

験 S および S1)の両⽅の⽅法を含む、3 つの試験サイト(ロチェスターエレクトロニクスと 2

つの外部試験委託会社)で個別に実施しました。また、J-STD-002 の要求事項に従い、試験

前に製品の端⼦を洗浄するなどの準備は⾏われませんでした。[3]

これらの製品を実装するために設計された基板は、3 つの製造委託業者とロチェスターエレ

クトロニクス社内にて組⽴てられました。各製造委託先で組⽴てられた基板は、外部の研究

所に送られ、断⾯解析と⾛査型電⼦顕微鏡(SEM)画像解析が⾏われました。電気的試験は、

基板実装⽤に選択された製品とは別の製品に対して実施されました。

© Rochester Electronic, Ltd.

4

Page5

4.IPC/JEDEC J-STD-002 はんだ付け性試験

4.1.ディップ&ルック試験

ディップ&ルック試験として知られるはんだ槽試験法は、機械装置を使⽤してフラックスと

溶融はんだにリード線を浸します。ロボット浸漬アームとはんだポットにより、浸漬速度と

引き上げ速度、滞留時間、温度を正確に制御することができます。はんだ付けされたリード

は、⾮濡れ、脱濡れ、およびピンホールの証拠がないか、拡⼤下で評価が実施されます。サ

ンプリングされたリードのいずれかが、基盤取り付けのための重要な領域にわたってこれら

の⽋陥が 5%以上を⽰した場合、そのロットははんだ付け性試験にて不合格であったとみな

されます。[3]

この試験は、THT 製品のウェーブはんだ実装をシミュレートしているにもかかわらず、表

⾯実装製品の試験でも、広く業界で使⽤されています。この理由としては、ロボットはんだ

付け性試験装置が普及していること、そのような装置によって部分的な⾃動化が可能である

こと、そして試験が⽐較的単純であることによるものと考えられます。そのためこの⽅法

は、推奨される SMT シミュレーション試験との⽐較分析のために含められました。

これらの古い表⾯実装製品のディップ&ルック試験では、様々な結果を得ることができまし

た。試験を⾏った 24ロットのうち、7ロットで J-STD-002 の不合格基準を超える⽋陥を発

⾒しました。属性の⼀致分析に基づくと、これらの結果は試験サイト間で良好から優れた⼀

致を⽰しました。図 2 は、不合格となった製品の代表的な画像を⽰しています。

図 2.ディップ&ルック試験に不合格となった SOIC 製品にみられるディウェッティングの例

4.2.SMT シミュレーション試験

SMT シミュレーション試験法は、1998年に業界標準に定義され[5]、表⾯実装製品の実際

の PCB 組⽴に近い⼿順を使⽤します。はんだ槽浸漬とは対照的に、フラックスを含むはん

だペーストは、製品のランドパターンに合わせて設計されたステンシルを使⽤して、セラミ

© Rochester Electronic, Ltd.

5

Page6

ック基板に塗布されます。製品は、印刷されたはんだペーストパターン上に配置され、製品

の端⼦仕上げ(SnPbと Pb フリー)に適した温度プロファイルを使⽤してリフローされま

す。リフロー後、フラックス残留物は除去され、ディップ&ルック試験と同じ基準で製品を

検査します。

SMT シミュレーション試験は、ディップ&ルック試験ほど業界では広く採⽤されておら

ず、この⽅法を提供している試験サイトは限られています。その理由としては、信頼性の⾼

いリフローの資⾦コスト、ステンシルの取得と管理にかかる運⽤コスト、保存期間が限られ

ているはんだペーストの⼩ロットの取り扱いにかかるコスト、およびこの状況におけるペー

ストの堆積と製品のピックアンドプレースのための標準化され⾃動化された装置の⽋如など

が挙げられます。

この⽅法は表⾯実装製品には好ましいですが、選択されたサンプルはディップ&ルック試験

に⽐べて試験性能の顕著な改善は⽰しませんでした。不合格は 43 ロット中 12 ロットで確

認されましたが、これはディップ&ルック試験で観察された割合とほぼ同じでした。結果は

3 つの試験間で中程度の相関性が⾒られました。特筆すべきは、2 つの試験⽅法の間の相関

関係はごくわずかで、多くの製品が⽚⽅の試験で不合格となりましたが、もう⽚⽅の試験で

は不合格となりませんでした。図 3 は、ディップ&ルック試験では合格だったものの、

SMT シミュレーション試験では不合格となった製品の代表例を⽰しています。

図 3.QFN製品の露出パッドで最⼤ 20%を超えるノンウェット

© Rochester Electronic, Ltd.

6

Page7

4.3.リード前処理⽅法(ベーキング式前処理と蒸気式加湿処理の⽐較)

適⽤されるはんだ付け性試験⽅法に関係なく、J-STD-002[3]では、製品のユーザーと部品

メーカーの間で別段の指定がない限り、前処理⼿順の使⽤が義務付けられています。はんだ

付け性試験が基板実装時の製品の有効性を評価するように設計されているのと同様に、前処

理は、PCB 組⽴で使⽤する前に製品の経年劣化をモデル化することを⽬的としています。

デフォルトの要件は、試験後に製品端⼦のはんだ付け性が“6か⽉を超える保管または複数

回の熱暴露により劣化する可能性がある”というシナリオを⽰すことを⽬的としています。

2013 年に発⾏された改訂D版以前は、蒸気式加湿処理が唯⼀の⽅法でした。錫含有鉛仕上

げの⼀般的な要件は、飽和温度よりわずかに低い蒸気に 8 時間暴露することでした。その

後の改定 Dおよび E 版(2017年)では、追加のベイク前処理⽅法として、155℃のドライベ

イクに 4 時間暴露する⽅法が追加されました。このベイク前処理は、蒸気式加湿処理に代

わるデフォルトの必須⽅法となり、蒸気式加湿処理の所要時間はすべて“オプションのレガ

シー”条件として記載されました。はんだ付け規格の改定履歴の詳細について、詳しくは図

4を参照してください。

図 4.PCB 組⽴との整合に向けたはんだ付け性規格改定の進展

リードを⼈⼯的に事前に劣化させるこれらの⽅法には、はんだ付け性試験が製造後すぐに実

施されること、つまり試験時には劣化が⾃然にはほとんど、あるいはまったく発⽣していな

いことが暗黙の前提となっています。この慣⾏は業界のほとんどに当てはまり、はんだ付け

性試験は、製品認定中に半導体メーカーによって実施される、または受⼊品質評価の⼀環と

してユーザーによって実施されます。

ロチェスターエレクトロニクスは製造中⽌品の正規販売代理店という独⾃の⽴場にあるた

め、さまざまな期間保管された後の製品にはんだ付け性試験を頻繁に実施しています。すで

に⻑期保管された製品に対しはんだ付け性試験を実施する場合、前処理⼯程を完全に省略す

る⽅が適切な場合があります。ロチェスターエレクトロニクスでは、この点を将来の可能性

のある⽅向性として調査します。この検証では、業界の⼀般的な⽅法論に基づいたアプロー

チで J-STD-002 に従うことに重点を置きました。

© Rochester Electronic, Ltd.

7

Page8

10年以上にわたってベーキング式前処理がデフォルトの⽅法として定義されているにも関

わらず、業界では、部品メーカー、ユーザー、およびサードパーティーの試験サイトでのデ

フォルトの⼿順として、蒸気式加湿処理が依然として⼀般的に使⽤されています。

そのため、本調査では、⼀般的な⽅法の幅広さを表すために、ベーキング式前処理及び蒸気

式加湿処理の両⽅の⽅法が選択されました。

4.4.繰返し性と再現性

使⽤された 3 つの試験サイトと評価された合計 67のサンプルロット全体を通して、ディッ

プ&ルック試験と SMT シミュレーション試験の両⽅で中程度の再現性の結果しか観察され

ず、サンプル全体で⼀貫して不合格となった製品はほどんどありませんでした。これは、⻑

期保管後のロット内製品間固有のばらつきに起因する可能性があります。図 2 でディップ

&ルック試験に不合格となった同じ製品が SMT シミュレーションに合格し、図 3 で SMT

シミュレーションに不合格となった同じ製品がディップ&ルック試験に合格した例を図 5

で⽰します。

図 5.SMT シミュレーションに合格した図 2 の SOIC 製品の代表的なリードと、

ディップ&ルック試験に合格した図 3 の QFN製品の例

ディップ&ルック試験では良好な再現性が観察されましたが、SMT シミュレーション試験

では中程度の再現性が得られました。これは、はんだペーストの堆積と製品の位置合わせが

⼿作業であること、また故障基準評価の細部で不⼀致があることが原因であると考えられま

す。特定の結果は SMT シミュレーション試験特有のものであり、ディップ&ルック試験に

は現れません。例えば、隣接する 2本のリードに塗布するはずのはんだペーストが、ペー

スト塗布時、ステンシル除去時、あるいは微細ピッチ製品の製品配置中にわずかなせん断運

動が発⽣すると、1本のリードに蓄積されることがあります。その⼀例の写真を図 6に⽰し

ています。同様の状況を解釈するには、標準的な要求事項を超える追加分析が必要となる場

合があります。そのため、結果は施設によって異なる可能性があり、再現性の課題の⼀因と

なる可能性があります。

© Rochester Electronic, Ltd.

8

Page9

図 6.対象QFN端⼦から⾮対象(すでにはんだ付けされている)

端⼦へのペーストの移動を⽰すはんだ厚さ測定結果

はんだ付け不良と製品の経年劣化との間には相関関係は認められませんでした。

5.プリント基板組⽴

IPC-A-610[6]認定を受けた 3 つの独⽴した委託製造業者が、カスタム設計の PCB にこれら

の製品を組み⽴てる担当として選ばれました。さらに、ロチェスターエレクトロニクスは、

SMT シミュレーション試験と同じリフローパラメータを使⽤して基板実装も⾏いました。

合計で 1,500 個以上の製品を組み込んだ 40枚の基板が組み⽴てられましたが、不合格品は

⾒つかりませんでした。実装された基板光学画像の例を図 7に⽰しており、良好なはんだ

接合部を外部から確認することができます。

図 7.ガルウィングリード、はんだボール、

およびはんだパッドの PCBへの接合⾯の光学画像

© Rochester Electronic, Ltd.

9

Page10

6.部品実装後の基盤の断⾯検査と電⼦顕微鏡検査

製造受託業者 3社により組⽴済みの基板は、外部の研究所で断⾯解析と⾛査型電⼦顕微鏡

解析が実施されました。この分析は、製品端⼦から PCB までのはんだ接合部の状態を確認

すること、および⻑期保管後の内部機械的完全性に関する以前の検証結果[2]を検証するこ

とを⽬的としています。

13 種類の異なる基板実装製品の代表サンプルとして、3 つの製品を選んで断⾯検査を⾏い

ました。断⾯検査された製品には、はんだ付け性試験に合格したものと不合格のもの両⽅が

含まれていました。図 8に⽰すように、3 つの組⽴拠点の基板で実⾏されたすべての断⾯検

査と SEM イメージングで、はんだ接合部は堅牢であることが確認されました。はんだ付け

性試験の結果が合格または不合格の製品間、あるは 3 つの委託製造業者の PCB 組⽴拠点間

で差異は観察されませんでした。

図 8.基板実装された 240 個の BGAと、20 個の TSSOP 製品の断⾯を⽰す SEM画像の代表例

パッケージの内部構造も断⾯観察と SEM で検証され、以前のロチェスターエレクトロニク

スのホワイトペーパー[2]の結果と同じでした。

7.電気的試験

2009年から 2016年に製造された各 30 個の表⾯実装製品(48リード TSSOP、14リード

SOIC、16リード SOIC パッケージ)からなる 4つのサンプルを、電気的試験のために新たに

使⽤しました。故障は発⾒されず、電気的性能は⻑期保管の影響を受けないというロチェス

ターエレクトロニクス[2]などによる以前の検証結果[7]を裏付けるものとなりました。

© Rochester Electronic, Ltd.

10

Page11

8.まとめ

本検証は、標準的なはんだ付け性試験⽅法が⻑期保管後の製品の基板性能と相関しない可能

性があるという直感に反する結論を⽰唆しています。この不調和は、はんだ付け性試験⽅法

が製造されたままの製品を使⽤して開発されたことに起因している可能性が⾼いです。ここ

で説明するように該当する PCB に部品を直接実装する⽅法は、製品の使⽤条件をより正確

にシミュレーションしています。

これは、2017年 11⽉に発⾏された J-STD-002 の最新改訂版と⼀致しており、鉛フリー

SMT シミュレーション試験(試験 S1)⽅法が定義されている 4.2.9 項に注記が追加されてい

ます。⽂字通り、"プリント基板への物理的な製品実装という観点から、SMT の実際の実証

は、SMT シミュレーションの代わりに、⽂書化された組⽴⼯程の⼀部として実施されるは

んだ付け性検査作業の⼀部として利⽤することができる"。 というものです。基板実装時の

性能は、はんだ付け性の最も重要な考慮事項です。

すでに製品の可⽤性とサプライチェーンの継続性の問題に直⾯している⻑期システムのユー

ザーにとって、各製品は⻑い製品ライフサイクルを⽀えるために⾮常に重要です。従来のは

んだ付け性試験⽅法を受⼊検査時のスクリーニングとして使⽤することは、利⽤可能な製品

の限られた制約に、さらに不必要な制約を課すことになりかねません。したがって、古い半

導体製品のユーザーは、検査⼿順を確⽴する際に、完全に機能し、はんだ付け可能な製品を

過剰に不合格にするリスクを考慮する必要があります。

ロチェスター エレクトロニクスの⻑期保管に関する検証は、4年以上にわたる試験、数⼗

種類の製品、および 4つの異なる年代に製造された製品に及んでいます。その⽅法論に

は、電気的試験、⾮破壊X線検査、はんだ付け性試験、パッケージ分解分析、PCB 組⽴、

断⾯検査、SEM イメージング、および外観検査などが含まれます。ロチェスターでの⻑期

保管による製品の機能性や使⽤性の低下を⽰すデータは⾒つかっていません。したがって、

これらの結果は、デートコードの制限を裏付ける証拠はないという業界の⼀般的な理解

[8]、[9]を補強するものとなります。

© Rochester Electronic, Ltd.

11

Page12

参考情報

[1] “The Effects of Long-Term Storage on Solderability of Semiconductor Components,”

Rochester Electronics, Newburyport, MA, USA, White Paper, 2021. [Online]. Available:

https://rocelec.widen.net/s/c8rgmj7qf6/re-white-paper_the-effects-of-long-term-storage-

on-solderability-of-semiconductor-components

[2] “The Effects of Long-Term Storage on Mechanical Integrity and Electrical Performance of

Semiconductor Components,” Rochester Electronics, Newburyport, MA, USA, White Paper,

2022. [Online]. Available: https://rocelec.widen.net/s/xxrfzwsxkg/effects-of-long-term-

storage-on-mechanical-integrity-and-electrical-performance_wp

[3] Solderability Tests for Component Leads, Terminations, Lugs, Terminals and Wires,

EIA/IPC/JEDEC J-STD-002E, IPC Int., Bannockburn, IL, USA, Nov. 2017.

[4] Mechanical Test Methods for Microcircuits, MIL-STD-883-2 w/ CHANGE1, Defense Logistics

Agency, Columbus, OH, Jan. 2022. [Online]. Available:

https://landandmaritimeapps.dla.mil/Downloads/MilSpec/Docs/MIL-STD-883/std883-2.pdf

[5] Solderability Test Method, EIA/JESD22-B102-C, Electronic Industries Alliance, Arlington, VA,

USA, Sep. 1998.

[6] Acceptability of Electronic Assemblies, IPC-A-610J, IPC Int., Bannockburn, IL, USA, Mar. 2024.

[7] R. R. Madsen, “Component Reliability After Long Term Storage,” Texas Instruments, Dallas,

TX, USA, SLVA304, 2008. [Online]. Available: https://www.ti.com/lit/wp/slva304/slva304.pdf

[8] Managing Date Code Restrictions on Orders for Electronic Components, GIPC #101,

Electronic Components Industry Assoc., Alpharetta, GA, USA, Jun. 2023. [Online]. Available:

https://ecia.memberclicks.net/assets/docs/managing%20date%20code%20restrictions%20ju

ne%202023.pdf

[9] “Are You Overthinking Date Codes?” Rochester Electronics. Accessed: Jun. 2024. [Online].

Available: https://www.rocelec.com/news/are-you-overthinking-date-codes

© Rochester Electronic, Ltd.

12