1/7ページ

ダウンロード(3.4Mb)

シミュレーションから実測までをつなぐ 高速デジタルチャネル設計の考え方

高速デジタル通信では、わずかな信号劣化が誤動作や性能低下の原因となります。本資料では、シグナルインテグリティー(SI)の基礎概念から、チャネルシミュレーション、アイダイアグラムによる評価、Sパラメータを用いた信号劣化要因の特定までを体系的に解説。

さらに、イコライゼーション設計、VNAによる実測、校正・ディエンベディングを含む測定ワークフローを紹介し、設計段階と実測結果を確実につなぐ方法を示します。高速デジタル/データセンター/SerDes設計に携わるエンジニア必読の基礎ホワイトペーパーです。

このカタログについて

| ドキュメント名 | 高速デジタル設計の成否を分ける。 シグナルインテグリティーの基礎と実践ガイド |

|---|---|

| ドキュメント種別 | ホワイトペーパー |

| ファイルサイズ | 3.4Mb |

| 登録カテゴリ | |

| 取り扱い企業 | キーサイト・テクノロジー株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

W H I T E P A P E R

シグナルインテグリティーの基礎

シミュレーションから実測まで

データセンターの送信/受信システム内のチャネルは、正確かつ効率的に情報を伝達する

ために重要です。チャネル内のデバイスの性能が低いと、シグナルインテグリティーの問

題が生じ、データの伝送に問題が生じる可能性があります。このため、チャネルを構成す

本記事の主な内容:

るデバイスやインターコネクトの開発では、優れたシグナルインテグリティーを確保する

ことが不可欠です。デバイス内のシグナルインテグリティー問題の原因を発見し、修正す • チャネルシミュレーション

ることは、きわめて困難な作業です。この記事では、優れたシグナルインテグリティーを • 信号劣化の根本原因の判定

備えたデバイスをデザインするための、シミュレーションと測定に関する推奨事項を記し • シグナルインテグリティー

ます。 の解決策の探索とデザイン

• シグナルインテグリティー

デジタル通信チャネルの代表的な例として、CPU(中央処理装置)からLED(発光ダイオード) 測定解析

ディスプレイまでの情報の送信を考えてみましょう。チャネルとはCPUとディスプレイの

間にあるすべてを指し、グラフィックスカード、ケーブル、オンボード・ビデオ・プロセッ

サといったインターコネクトデバイスが含まれます。すべてのデバイスと、チャネル内の

デバイス間の接続は、CPUから送信されるデータに対して妨害や干渉を引き起こす可能性

があります。

シグナルインテグリティーの問題には、クロストーク、遅延、リンギング、電磁波干渉といっ

た多様な原因があります。シグナルインテグリティーの問題に早期に対処することで、信

頼性が高くコストが低い高性能な製品を開発できます。

www.keysight.co.jp 1

Page2

チャネルシミュレーション

エレクトロニック・デザイン・オートメーション・ソフトウェアを使用して、回路シミュレーション

を作成します。デザイン・オートメーション・ソフトウェアは、ビット単位および統計シミュレーショ

ン技術を使用することで、高速で正確なチャネルシミュレーションを実現できます。マルチギガビッ

ト・シリアル・リンク(送信から受信まで)のシミュレーションを容易にするために、デザインソフト

ウェアではアルゴリズミック・モデリング・インタフェースが標準として用いられます。

シミュレーションソフトウェアに加えて、アイダイアグラム、ミックスドモードSパラメータ、タイ

ムドメインリフレクトメトリ、信号パルス応答といった信号解析ツールを使用します。トランスミッ

ターからレシーバーまでのデータ伝送をシミュレートする際は、オシロスコープで用いられるような

アイダイアグラムを解析ツールとして使用することで、チャネルの性能を評価できます。

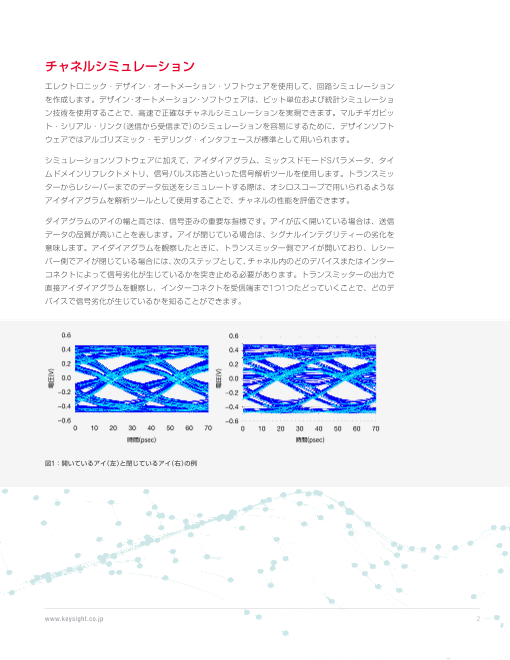

ダイアグラムのアイの幅と高さは、信号歪みの重要な指標です。アイが広く開いている場合は、送信

データの品質が高いことを表します。アイが閉じている場合は、シグナルインテグリティーの劣化を

意味します。アイダイアグラムを観察したときに、トランスミッター側でアイが開いており、レシー

バー側でアイが閉じている場合には、次のステップとして、チャネル内のどのデバイスまたはインター

コネクトによって信号劣化が生じているかを突き止める必要があります。トランスミッターの出力で

直接アイダイアグラムを観察し、インターコネクトを受信端まで1つ1つたどっていくことで、どのデ

バイスで信号劣化が生じているかを知ることができます。

0.6 0.6

0.4 0.4

0.2 0.2

0.0 0.0

−0.2 −0.2

−0.4 −0.4

−0.6 −0.6

0 10 20 30 40 50 60 70 0 10 20 30 40 50 60 70

時間(psec) 時間(psec)

図1:開いているアイ(左)と閉じているアイ(右)の例

www.keysight.co.jp 2

電圧(V)

電圧(V)

Page3

信号劣化の根本原因の判定

デバイスの周波数動作を記述するための業界標準は、Sパラメータです。インターコネクトのSパラ

メータは、タイムドメインと周波数ドメインのどちらで測定された場合でも、インターコネクトのビ

ヘイビアモデルを表現することができます。これらのパラメータには、1つのポートから入った信号

が別のポートから出る際の挙動に関するすべての情報が含まれます。

信号劣化の根本原因を特定するには、まずSパラメータの期待値を仮定することが重要です。期待値

と測定値を比較することで、シグナルインテグリティーの劣化を引き起こしているチャネルの部分を

特定できます。

次に、デバイスまたはインターコネクトを詳細に観察して、根本原因を判定します。差動チャネルの

場合は、ミックスドモードSパラメータを使用した解析によって根本原因を突き止めます。最も一般

的なSパラメータとしては、差動リターンロス(SDD11)、差動挿入損失(SDD21)、差動/コモンモー

ド変換(SCD21)が挙げられます。これらは電磁波干渉や結合に関連しています。

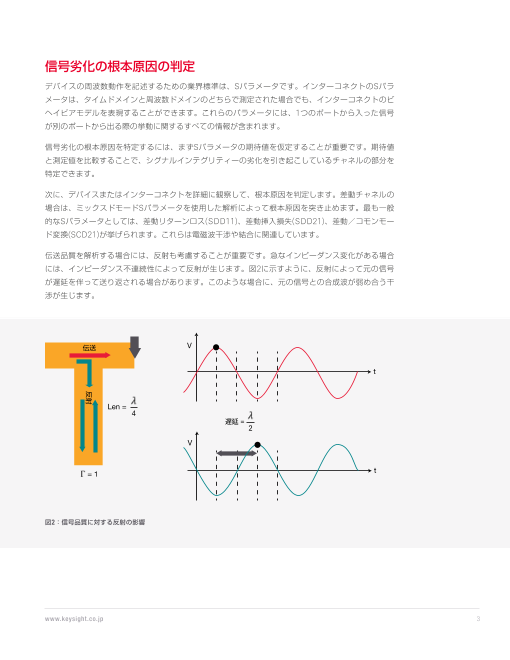

伝送品質を解析する場合には、反射も考慮することが重要です。急なインピーダンス変化がある場合

には、インピーダンス不連続性によって反射が生じます。図2に示すように、反射によって元の信号

が遅延を伴って送り返される場合があります。このような場合に、元の信号との合成波が弱め合う干

渉が生じます。

伝送 V

t

Len =

4

遅延 =

2

V

= 1 t

図2:信号品質に対する反射の影響

www.keysight.co.jp 3

反射

Page4

シグナルインテグリティーの解決策の探索とデザイン

信号劣化の根本原因がわかったら、可能な修正方法を調べ、最善の解決策を見つける必要があります。

まず、問題の部分をデザインから除去してシミュレーションを行い、それが実際にシグナルインテグ

リティーの劣化の根本原因であることを確認します。解決策としては、問題の部分を除去するのでは

なく、レシーバー側にイコライゼーションを追加することを検討します。例えば、デシジョン・フィー

ドバック・イコライゼーション(DFE)、周波数ドメインの連続時間リニアイコライゼーション、タイ

ムドメインのフィードフォワードイコライゼーションなどが使用できます。もう一度シミュレーショ

ンを使用して、イコライゼーションを追加し、オシロスコープで用いられるアイダイアグラムが開く

かどうかを観察して、シグナルインテグリティーの問題が解決されていることを確認します。

もう1つのテスト方法としては、図3に示すように、イコライゼーションを使用する前後のアイ開口部

にマスクを適用し比較することもできます。イコライゼーションを追加する前には、イメージがマス

クに抵触しており、アイ中心の開口部が閉じていることがわかります。イコライゼーションを追加し

た後では、イメージはマスクに抵触しておらず、アイが開いていることがわかります。

0.20 0.20

0.15 イコライゼーションなし 0.15 イコライゼーションあり

0.10 0.10

0.05 0.05

0.00 0.00

−0.05 −0.05

−0.10 −0.10

−0.15 −0.15

−0.20 −0.20

20 25 30 35 40 45 50 55 15 20 25 30 35 40 45 50

時間、psec 時間、psec

図3:DFEの適用前後のアイマスクの比較

シグナルインテグリティー測定解析

製品のデザインがシミュレーションからハードウェアの段階に進むと、高速デジタルインターコネク

ト評価のためにベクトル・ネットワーク・アナライザ(VNA)が必要になります。初めに、チャネル、

物理層デバイス、コネクタ、ケーブル、バックプレーン、またはプリント回路基板に期待される測定

結果を事前にシミュレーションしておきます。この情報は、実測結果が得られたときに比較する対象

となります。目標は、ソフトウェアによるシミュレーションとハードウェアによる実測の両面で信頼

性の高いシグナル・インテグリティー・ワークフローを確立することです。ハードウェア測定の手順

として、測定器の測定セットアップ、チャネルデータの収集、チャネル性能の解析があります。

VNAのようなダイナミックレンジの広い測定器の場合、正確なSパラメータ測定結果を得るために、

誤差補正について理解しておくことが重要です。誤差補正には、校正(測定前の誤差補正)とディエン

ベディング(測定後の誤差補正)の両方が含まれます。校正とディエンベディングが適応される基準面

において、被測定物(DUT)以外のチャネル内すべての誤差成分を除去するように調整します。以下、

校正とディエンベディングによる誤差補正の違いと、それらの適応方法を示します。

www.keysight.co.jp 4

電圧(V)

電圧(V)

Page5

校正

VNAの電源を立ち上げた状態では、基準面はデフォルトでフロントパネルのコネクタ端面になります。

DUTとの接続の必要なケーブルを追加した状態では、ケーブルの影響を除去するように校正面を移動

させる必要があります。そのためには、ショート/オープン/ロード/スルー (SOLT)、スルー反射

ライン、またはスルー反射マッチ校正基準を使用します。SOLTが最も一般的な方法です。

ケーブルはDUTに直接接続されるか、フィクスチャに接続されます。フィクスチャは、同軸ケーブル

とDUTの間に配置され、異なる種類のコネクタへの変換を行います。例えば、HDMI、DisplayPort、

シリアルATA、PCI Expressなどです。これから示す例の場合、同軸ケーブルは校正基準面の内側に

含まれ、ディエンベディング適応対象にフィクスチャが含まれている必要があります。校正とディエ

ンベディングを組み合わせた誤差補正を適応する対象には、DUTまでのチャネル内のすべてのイン

ターコネクトが含まれる必要があります。DUTを接続したら、測定を実行し、測定後の誤差補正(ディ

エンベディング)を行います。

校正

新基準面

DUT

図4:校正テストセットアップと基準面

www.keysight.co.jp 5

Page6

ディエンベディング

測定を実行したら、ディエンベディング基準面をDUTの入力と出力に設定し、テストフィクスチャの

影響を除去します。テストフィクスチャを除去することにより、フィクスチャによってシステムに負

荷された損失と反射が補正され、正確なSパラメータ測定でデバイスを表現することができます。

2段階(校正とディエンベディング)の補正後のSパラメータ結果を期待される結果と比較することで、

実際の測定値に合わせてシミュレーションモデルを調整し、デバイスの開発を進めることができます。

コネクタ コネクタ

+ +

基準面

P1 P2

ディエンベディング DUT ディエンベディング

P3 P4

図5:ディエンベディング・テスト・セットアップと基準面

www.keysight.co.jp 6

Page7

シグナルインテグリティーの問題の解決

送信データ速度の高速化とともに、チャネルのデバイスやインターコネクトには優れたシグナ

ルインテグリティーが不可欠になっています。デバイスで優れたシグナルインテグリティーを

実現するには、まず期待されるシミュレーションおよび測定結果を仮定し、実測結果と比較し

ます。

次に、オシロスコープ測定で使われるアイダイアグラムなどの信号解析技法とシミュレーショ

ンソフトウェアの組み合わせを使用して、信号劣化の根本原因を突き止めます。シグナルイン

テグリティーの問題に対処するための解決策をデザインしたら、シミュレーションと実測の両

面で信頼性の高いシグナル・インテグリティー・ワークフローを確立する必要があります。

適切なVNAを使用して校正基準面を設定し、Sパラメータ測定を実行し、ディエンベディング

を適応することでフィクスチャを正しく除去します。その結果、正確なSパラメータと、デバ

イスを信頼性高く表現することができます。早い段階でシグナルインテグリティーの問題に対

処することで、回路デザインを最適化し、高い信頼性と妥当なコストで動作するデバイスを実

現できます。

関連リンク

• データセンターのトランシーバーのテスト

• 高速デジタルシステム設計

詳細情報:www.keysight.co.jp

キーサイト・テクノロジー株式会社

本社〒192-8550 東京都八王子市高倉町9-1

計測お客様窓口

受付時間 9:00-12:00 / 13:00-18:00(土・日・祭日を除く)

TEL:0120-421-345 (042-656-7832) | Email:contact_japan@keysight.com

本書の情報は、予告なしに変更されることがあります。 © Keysight Technologies, 2019, Published in Japan, October 23, 2019, 5992-4324JAJP 7