1/31ページ

ダウンロード(695.9Kb)

MCZ5205SE|アクティブスタンバイ機能で待機電力低減|OA機器・LED照明・産業用電源に最適

MCZ5205SEは、電流臨界型PFC制御とLLC電流共振ブリッジコンバータ制御をワンチップ化したICです。600V耐圧ゲートドライバを内蔵し、ハイサイドMOSFETを直接駆動可能。共振はずれ保護、過電流・過熱・ブラウンアウト保護を標準搭載し、高効率・低ノイズ、省スペース化に貢献します。さらにアクティブスタンバイ機能で軽負荷時の損失を低減し、OA機器、LED照明、産業用電源、TV電源に最適です。

このカタログについて

| ドキュメント名 | アプリケーションノート|MCZ5205SE|600V耐圧・PFC+LLC制御 スイッチング電源制御IC |

|---|---|

| ドキュメント種別 | ハンドブック |

| ファイルサイズ | 695.9Kb |

| 取り扱い企業 | 新電元工業株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

CAT.No. 1H0300-3

MCZ5205SE APPLICATION NOTE JUN.2019 Ver1.1

PFC機能搭載

LLC電流共振ブリッジコンバータ

制御 IC

MCZ5205SE

アプリケーションノート ver. 1.1

新電元工業株式会社

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 1 -

Page2

MCZ5205SE

Standard Power 使用上の注意

Supply

このたびは、弊社製品をご使用いただき誠にありがとうございます。

当 ICをご使用の際は、お客様の安全を確保するため下記の警告ならびに注意を必ず守ってご使用下さい。

警

誤った取り扱いをしたときに死亡や重大な人身事故および大きな物的損害に結びつく危険性のあるもの。

告 !

注

誤った取り扱いをしたときに軽傷に結びつく恐れ、または軽微な物損事故に結びつく恐れのあるもの。

意 !

警 当 ICは、一般電子機器(事務機器・通信機器・計測機器・家電製品等)に使用されることを意図しております。誤動作や事

故が直接人体や生命を脅かす恐れのある医療器、航空宇宙機、列車、輸送機器(車載、船舶等)、原子力等の制御機器

告 ! には使用しないで下さい。一般電子機器以外にご使用になる場合は弊社までご相談下さい。

修理や改造は、重大な事故につながりますので、絶対にやめて下さい。

! 《感電、破壊、火災、誤動作等の危険があります。》

異常時は出力端子に過大電圧が発生したり、電圧低下となる場合があります。 異常時の、負荷の誤動作や破壊等を想定

! した保護対策(過電圧保護、過電流保護等の保護対策)を最終機器に組み込んで下さい。

注

入力端子、出力端子の極性を確認し誤接続の無いことを確認してから通電して下さい。

意 ! 《保護素子が切れたり、発煙・発火の原因になります。》

! 決められた入力電圧を必ず守っていただくとともに、入力ラインに必ず保護素子を挿入して下さい。

《異常時には発煙・発火の危険があります。》

! 使用中に故障または、異常が発生した時は、すぐに入力を遮断して電源を停止させて下さい。また、直ちに弊社にご相談

下さい。

●本資料に記載されている内容は、製品改良などのためお断りなしに変更することがありますのでご了承下さい。

●御使用頂く際には、仕様書の取り交わしをして頂けます様お願いします。

●ここに記載されたすべての資料は正確かつ信頼し得るものでありますが、これらの資料の使用によって起因する損害または特許権その

他権利の侵害に関しては、当社は一切その責任を負いません。

●本資料によって第三者または当社の特許権その他権利の実施に対する保証または実施権の許諾を行うものではありません。

●本資料の一部または全部を当社に無断で転載または複製することを堅くお断りいたします。

! 当社は、品質と信頼性の向上に絶えず努めていますが、半導体製品はある確率で故障が発生したり、誤動作する場合があります。必要

に応じ、安全性を考慮した冗長設計、延焼防止設計、誤動作防止設計等の手段により結果として人身事故、火災事故、社会的な損害等が

防止できるようご検討下さい。

! 本資料に記載されている当社半導体製品は、特別に高い品質・信頼性が要求され、その故障や誤動作が直接人命を脅かしたり、人体

に危害を及ぼす恐れのある機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。下記の特別用途、

特定用途の機器、装置にご使用の場合には必ず当社へご連絡の上、確認を得て下さい。

特別用途

輸送機器(車載、船舶等)、基幹用通信機器、交通信号機器、防災/防犯機器、各種安全機器、医療機器 等

特定用途

原子力制御システム、航空機器、航空宇宙機器、海底中継器、生命維持のための装置 等

! なお、IC製品に関しては、特別用途・特定用途に限らず、連続運転を前提として長期製品寿命を期待される機器、装置にご使用される

場合に関しては当社へお問い合わせ下さい。

当社は IC製品を安全に使っていただくために回路支援をいたしています。弊社担当営業または商品企画

にお問い合わせ下さい。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 2 -

Page3

Index

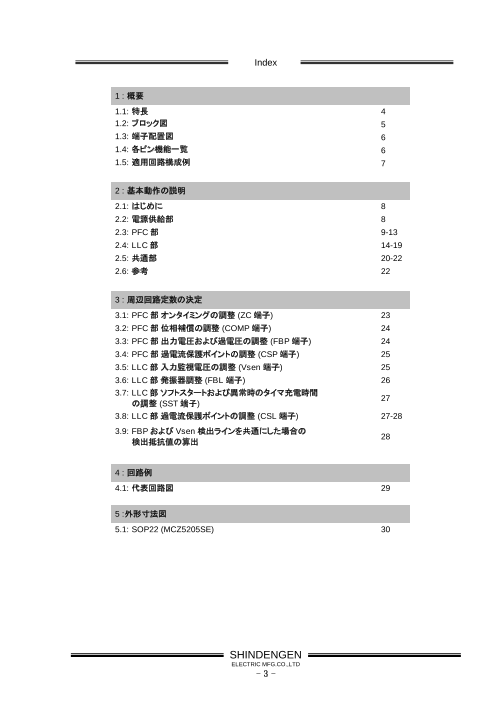

1 : 概要

1.1: 特長 4

1.2: ブロック図 5

1.3: 端子配置図 6

1.4: 各ピン機能一覧 6

1.5: 適用回路構成例 7

2 : 基本動作の説明

2.1: はじめに 8

2.2: 電源供給部 8

2.3: PFC部 9-13

2.4: LLC部 14-19

2.5: 共通部 20-22

2.6: 参考 22

3 : 周辺回路定数の決定

3.1: PFC部 オンタイミングの調整 (ZC端子) 23

3.2: PFC部 位相補償の調整 (COMP端子) 24

3.3: PFC部 出力電圧および過電圧の調整 (FBP端子) 24

3.4: PFC部 過電流保護ポイントの調整 (CSP端子) 25

3.5: LLC部 入力監視電圧の調整 (Vsen端子) 25

3.6: LLC部 発振器調整 (FBL端子) 26

3.7: LLC部 ソフトスタートおよび異常時のタイマ充電時間

27

の調整 (SST端子)

3.8: LLC部 過電流保護ポイントの調整 (CSL端子) 27-28

3.9: FBPおよび Vsen検出ラインを共通にした場合の

28

検出抵抗値の算出

4 : 回路例

4.1: 代表回路図 29

5 :外形寸法図

5.1: SOP22 (MCZ5205SE) 30

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 3 -

Page4

1 概要

MCZ5205SEは、臨界型 PFC(Power Factor Correction)制御用コントローラと、高耐圧ゲートドライバを有し

た周波数変調タイプの LLCブリッジ型全波電流共振電源制御用コントローラの 2つの制御回路を集積したコント

ローラ ICで、この 2つのコントローラを 1チップに内蔵することで省スペース化を図ることが出来ます。

PFC部は臨界 PFCを採用し、低ノイズ・高効率化を実現しています。

LLC部は共振はずれ防止機能等の各種保護機能を備え、高効率化を実現しています。

さらに、アクティブスタンバイ(AS)機能を有し、軽負荷待機時の電力損失を大幅に改善することが出来ます。

本 ICは、PFCおよび LLCをワンチップで搭載し、各種保護機能も備わっている為、設計の簡易化および省ス

ペース化を実現でき、以下の製品に最適です。

• PDP / LCD 等大画面フラット TV用電源

• レーザープリンタ等の OA機器用電源

• 大出力 ACアダプタ

• 大電力産業機器用電源

• ハイパワーLED照明

1.1 特長

[ 一般的な特長 ]

1. PFCと LLCの機能をコンボ化し、SOP22パッケージで実現。

2. アクティブスタンバイ機能を搭載し、軽負荷領域の損失低減に対応。

3. アクティブスタンバイ端子(外部ラッチ端子)を利用した過電圧ラッチ回路を構成可能。

4. PFC/LLC ON-OFFシーケンスを最適化。

5. Vcc耐圧は 35V、UVLOはヒステリシスを持ち 12.6V/8.5V。

[ PFC部特長 ]

1. 臨界型 PFCコントローラ。

2. 過電流検出しきい値は 0.5Vであり、検出抵抗ロス削減。

3. オン幅(電圧)制御により入力ライン検出不要。

4. フィードバックオープン・ショート保護、過電圧発振停止保護(OVP)、過熱保護(LLC部共通)、

軽負荷の時出力電圧上昇保護機能搭載。

[ LLC部特長 ]

1. ドライブ能力(Source 0.18A 、Sink 0.38A)最適化により、ゲート周りをシンプルに構成可能。

2. ハイサイドドライバ内蔵により MOSFETの直接ドライブが可能。

3. アクティブスタンバイモードで非対称スイッチング動作。

アクティブスタンバイモードにより非対称制御に切り替わり、軽負荷領域での損失を低減。

4. di/dt保護機能により、危険な di/dtモードを回避し MOSFETを保護。

5. 過電流保護(OCP)、di/dt保護(共振はずれ保護)、タイマーラッチ、不足電圧保護、過熱保護

(PFC部共通)等の各種保護機能搭載。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 4 -

Page5

1.2 ブロック図

VC2

ZC

On Trig Restart Time PFC Driver VGP

S

1 Q 22

S

Ton MAX / Off trig. R

PGND

TSD R R

COMP CSP

Ton Burst LEB

2 21

OVP

COMP short PFC

STOP OFF Trig

FBP open protection

FBP PGND

3 20

COMP short

FBP Latch

Vsen VC2

Driver Reg.

4 19

ASpin=low:Standby

Vc2 STOP

AS SS Reset

VC1

Vc1 Vc1 UVLO Internal Vref (NC)

5 18

OSC, Vfbl(top) Reset TSD

Fixed DT Vfbl(bottom)

Vfbl(msk)ocp/didt

FBL (NC)

Tss(3)

6 AS 17

Vc2 Load Reg

Soft Start

SST Voltage SST STOP COMP short (NC)

clamp

7 16

Counter reset COMP short

TSD

SGND Vss (NC)

R

8 15

LLC

Protection Counter S Q LLC High

Side Driver

LLC STOP

Timer x2 times S

Latch Control

STOP Logic Level

CSL Shift

VB

9 OCP detect OCP Counter 14

x1 & x2 times

x8 times AS Latch

S LLC Low

ASpin=low:Standby

di/dt detect Side Driver

ASpin=low:Standby

AS Voltage VC2

AS ON/OFF AS Counter VS

R Q

clamp x1 & x2 & x3 VGL

10 13

PGND

VGL VGH

VGL

11 12

図 1 . MCZ5205SE ブロック図

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 5 -

FB Latch

+

-

-

+

Page6

1.3 端子配置図

ZC 1 22 VGP

COMP 2 21 CSP

FBP 3 20 PGND

Vsen 4 19 Vc2

Vc1 5 18 NC

FBL 6 17 NC

SST 7 16 NC

SGND 8 15 NC

CSL 9 14 VB

AS 10 13 VS

VGL 11 12 VGH

図 2 . MCZ5205SE 端子配置図

1.4 各ピン機能一覧

端子番号 記号 コンバータ 機能

オンタイミング検出端子

1 ZC PFC

ゼロ電流を検出して、PFC部主 SWのオンタイミングを決めます。

フィードバックアンプの出力端子

2 COMP PFC

位相補償設定用の端子です。

フィードバックアンプの入力端子

3 FBP PFC

PFC出力電圧のフィードバック、低入力電圧監視を行います。

PFC出力電圧監視用端子

4 Vsen LLC

ブラウンアウト保護のため、低入力保護、リモート ON/OFF、SS-Resetを行います。

制御回路の電源供給端子

5 Vc1 共通

Vc1≧12.6Vで動作開始、Vc1≦8.5Vで動作停止します。

LLC部 発振器の周波数設定用端子

6 FBL LLC

外付けコンデンサ、抵抗により Dutyや動作周波数が決まります。

ソフトスタートと異常検出時の間欠動作用コンデンサ接続端子

7 SST LLC

ソフトスタート時間および異常検出時の間欠動作時間を決めます。

制御信号系 GND端子

8 SGND 共通

制御信号系の GND接続端子。

LLC部の過電流検出および di/dt(共振はずれ)保護機能用端子

9 CSL LLC

OCPおよび di/dtを検出して、過電流および共振はずれを保護します。

アクティブスタンバイ切り替え端子

10 AS 共通 端子ショート時、アクティブスタンバイモードで動作します。

外部入力ラッチ機能としても使用できます。

LLC部下側 MOSのゲート駆動用端子

11 VGL LLC

LLC部下側MOSのゲートを駆動します。

LLC部上側 MOSのゲート駆動用端子

12 VGH LLC

LLC部上側MOSのゲートを駆動します。

LLC部上側ドライバの基準電源端子

13 VS LLC

LLC部上側MOSのソースおよび下側 MOSのドレインに接続。

LLC部上側ドライバの電源端子

14 VB LLC

LLC部上側ドライバ駆動用電源端子。

15-18 NC - 沿面距離確保の為の空きピン

ドライバ用電源出力端子

19 Vc2 共通

PFCおよび LLC MOSゲート駆動用電源出力端子。

パワー系 GND端子

20 PGND 共通

パワー系の GND接続端子。

PFC部過電流検出端子

21 CSP PFC

PFC部主 SWの過電流を検出します。

PFCゲート出力端子

22 VGP PFC

PFC部主 SWの駆動用。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 6 -

SHINDENGEN

MCZ5205

Page7

1.5 適用回路構成例

図 3 . 基本構成例

AC-IN(N) 1

AC-IN(L) 2

+ +

+

Vout-1

+

RTN

VGP CSP P Vc 2 NC NC NC NC VB VS VGH

GND

MCZ5205SE

S

ZC COMP FBP Vsen Vc1 FBL SST CSL

ND AS VGL

G

Vcc

Active STBY

図 4 . 基本構成例 (PFC を使用しない場合)

AC-IN(N) 1

AC-IN(L) 2

- +

Vout-1

+

RTN

+

VGP CSP P Vc 2 NC NC NC NC VB VS VGH

GND

MCZ5205SE

S

ZC COMP FBP Vsen Vc1 FBL SST CSL VGL

GND AS

Vcc

Active STBY

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 7 -

Page8

2 基本動作の説明

※ 特に指定がない場合は、しきい値等の数値は TYP表記しています。詳細は特性仕様書をご覧下さい。

2.1 はじめに

MCZ5205SEは、以下の主要ブロックから構成されています。各ブロックの動作については、2.2 項以降を

ご覧下さい。また、各機能の調整法については、3項以降をご覧下さい。

・ 電源供給部

電源供給部については、2.2項をご覧下さい。

・ PFC部

PFC部の動作および保護機能については、2.3項をご覧下さい。

・ LLC部

LLC部の動作および保護機能については、2.4項をご覧下さい。

・ 共通部 (アクティブスタンバイ機能、共通保護機能)

共通部の動作および保護機能については、2.5項をご覧下さい。

2.2 電源供給部

2.2.1 制御 IC電源供給(Vc1端子)

Vc1端子は、制御 IC電源供給用端子です。本端子から内部回路に電源供給されます。

Vc1端子には安定した電圧を供給する為、ICの近くで対 GND間にコンデンサを挿入します。

コンデンサ容量は、起動・切断などの過渡状態で安定する容量をご選定下さい。また、電源基板パター

ン等で Vc1端子にノイズが入り MCZ5205SEが誤動作する場合、Vc1-GND端子間直近に数μFの

MLCC等のコンデンサを挿入して下さい。

Vc1端子電圧が Vc1(start) 12.6V以上で Vc2端子への充電を開始し、内部回路が動き始めます。

Vc1端子電圧が Vc1(stop) 8.5V以下になると、Vc2端子は放電され ICは停止します。異常状態(タイマ

ーラッチなど)等でラッチ停止した場合、Vc1端子電圧を Vc1(latch reset) 8.1V以下にすることでラッチ解

除します。

2.2.2 ドライバ用電源出力 (Vc2端子)

Vc2端子は、ドライバ用電源出力端子です。本端子は、PFCおよび LLCそれぞれのゲート出力端子に

電圧を供給します。通常動作や起動・切断時等に安定したドライブを行う為に、Vc2-GND間にコンデンサ

を挿入します。(4.7uF-22uF程度を推奨します。)

コンデンサ容量は、起動・切断などの過渡状態で安定する容量をご選定下さい。

Vc1端子電圧が Vc1(start)まで到達すると Vc2端子に充電を開始し Vc2端子が Vc2(start) 9.6Vまで

到達すると FBL端子が発振開始してドライブ動作可能になります。

PFCおよび LLCのゲート出力動作開始条件は、2.3項および 2.4項をご覧下さい。

2.2.3 LLC部上側ドライバ電源 (VB端子)

VB端子は、LLC部ハイサイドドライバ用電源端子です。本端子は、Vc2端子よりブートストラップ用ダイ

オードを介して接続されます。ブートストラップ用コンデンサを VB端子と VS端子間に接続して下さい。

VB-VS間に接続されるコンデンサのコンデンサ容量は、起動・切断などの過渡状態で安定する容量をご

選定下さい。ブートストラップ用ダイオードには、高速かつソフトリカバリー特性を持った 600V以上(PFC

出力電圧を約 400Vとした場合。) のものを用いて下さい。弊社、D1NK60等を推奨いたします。

VB端子には、独立した低電圧保護機能を搭載しています。VB-VS間端子電圧が VB-VS(start) 7.4V

以上でハイサイドゲート出力開始、VB-VS(stop) 5.3V以下でハイサイドゲート出力停止します。このヒス

テリシスにより起動・切断時に安全で安定したドライブが可能となります

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 8 -

Page9

2.3 PFC部

2.3.1 PFCゲートドライバ (VGP端子)

PFCのゲート出力は VGP端子より行います。

VGP端子は、安定したドライバ電源電圧 Vc2 10.2Vから供給され、PFCゲートドライバ駆動能力は、

0.23A(Source)/0.6A(Sink)です。この値は、信号系誤動作を引き起こさずに MOSFETを十分高速にドラ

イブできるように設計されています。

一般的に用いられる駆動回路の例を図 5 に示します。

A)、B)の様に電荷引き抜き用ダイオードを用いる場合には小容量ショットキーダイオードなどを用い、ス

ナッピー(ハード)リカバリーダイオードは使わないように注意して下さい。推奨ダイオード例として 新電元

製 D1NS4(アキシャル)や M1FM3(面実装)があります。

また、Qgの大きい MOSFETを接続して引き抜きが十分でない場合、図 5 C)のように引き抜き側に

PNP トランジスタを使用して下さい。

A) B)

Q1 Q1

R2 D1 D1

Qa Qa

Qb Qb

VGP R1 VGP R1 R2

R3 R3

CSP CSP

検出抵抗 検出抵抗

GND GND

C)

Q1

Qa

R1 R2

Qb VGP

R3

CSP

検出抵抗

GND

図 5 . PFC部ゲート駆動回路

2.3.2 PFC出力電圧制御および過電圧検出

PFC 出力電圧は、PFC ゲートオン幅を制御することにより出力電圧を安定化しています。図 6 のように、

PFC出力電圧を分圧しその電圧を FBP端子で検出して内部リファレンス電圧 Vo(ref) 2.5V と比較する

事でフィードバックを掛けます。その結果、この FBP端子電圧が 2.5Vとなる出力電圧で一定に保たれま

す。

PFCは商用周波数に反応しないように応答を遅く設計します。そのため、起動時等の過渡的な状態で

は出力電圧が一時的に上昇する事があります。この対策として FBP端子電圧が Vfb(H) (Vo(ref)×1.10)

を上回ると、過電圧検出によりゲート出力停止致します(ラッチ停止ではありません)。これによって、出力

電圧の上昇を抑え電解コンデンサ等の回路部品を破壊から守る事ができます。

また、FBP端子-GND端子間直近にはノイズ対策として 1000pF程度のコンデンサを接続して下さい。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 9 -

Page10

PFC OUT

Ton MAX 27.5us

COMP Vo(ref)=2.5V

Ton / Burst 0.8V

Vo(ref)×1.10

PFC OFF

0.4V

FBP

COMP short

(発振停止)

図 6 . FBP端子内部ブロックと接続例

2.3.3 PFC部位相補償

COMP 端子はフィードバックアンプの出力端子であり、COMP 端子‐GND間にコンデンサを接続する事

でアンプの位相補償を行います。

COMP端子位相補償例を図 7に示します。COMPの調整方法は、3.2項をご覧下さい。

この端子電圧と主スイッチのオン時間幅には図 8のような関係が有り、フィードバックが掛かる事で適切

な COMP電圧(つまりオン時間幅)で一定に保たれます。なお、最大 ON時間は IC内部で固定されてお

り、Ton(max) 27.5usです。

更に COMP電圧が Vth(burst) 0.8V以下になるとオン幅が完全にゼロとなります。これにより、出力電圧

の上昇を防ぐことが出来ます。

COMP vs ON Time

Ton

max

COMP

発 発

RCOMP 振 振

停 開

CCOMP2 止 始

CCOMP1

0us

0.8V 4.0V

COMP電圧 [V]

図 7 . COMP端子接続例 図 8 . COMP電圧とオン幅の関係

SHINDENGEN

図 7 . COMP端子位相補正例 ELECTRIC MFG.CO.,LTD

- 10 -

オン幅Ton [us]

-

+

+

-

-

+

Page11

2.3.4 PFC臨界動作

PFC部は電流臨界動作方式を採用しており、メインチョークのコントロール巻線電圧を検出し スイッチ

ング素子のオンを行っています。このオンタイミングは ZC端子により決まります。

図 9のようにエネルギーの放出タイミングをコントロール巻線のネガティブエッジで検出し、Vzc(L)

0.55Vを下回ったタイミングで主スイッチング素子をオンすることで電流臨界動作を行っています。

また、この Vzc(L)に対して、Vzc(hys) 1.0Vのヒステリシスをもたせることにより耐ノイズ性を高めてい

ます。

さらに、本 ICにはゲートオフ時のリンギング電圧によってオントリガを検出してしまい電流臨界点よりも

はやくオンしてしまう誤動作を防止する為、ゲートオフ信号が出てからオントリガを禁止する期間 Tonデッ

ドタイム Tondead 800ns を設けています。これにより、ゲートオフ時のリンギングによる誤動作を防止し

ます。

1.55V

0.55V

【VZC】

幅1V

【IDP】

【ダイオード電流】

【VDS】

図 9 . PFC部 オンタイミング (ZC端子)

制御巻線-ZC端子間には、制限抵抗を挿入します。この抵抗には2つの役割があります。

① 主 SWオフ後の共振動作中、主 SWの Drain-Source間電圧が最下点(ボトム)でゲートを ONさせる。

臨界動作型 PFCにおいて、ダイオード電流が 0Aになったときにメインチョーク Lpと共振コンデンサ

(または MOSの Drain-Source間寄生容量)Cqによる共振周波数での減衰振動が始まります。このと

きの Cqの放電電流はメインチョークを通り入力側へエネルギーを返すように流れます。

この制限抵抗を調整することにより、減衰振動電圧の谷点で主 SW素子をターンオンさせることがで

きます。これにより、ターンオンロスを低減することが可能です。

② ZC端子流入・流出電流を制限する

ZC端子に流すことの出来る最大電流 Izcは+/-5mAであり、この電流値以内の制限抵抗を使用しま

す。制限抵抗値の設計方法は 3.1項をご覧下さい。

また、この抵抗値の上限値の目安として、アブノーマル対策等で ZC端子-GND間にツェナーダイオ

ードを接続する場合は、そのツェナーダイオードのリーク電流に十分注意し、オントリガに最低必要な

Vzc(H) 1.55V に対して十分マージンが取れている事を確認して下さい。

②から求められる Rzcの範囲で、①の役割(ボトム ON)を満たす抵抗値を選定して下さい。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 11 -

Page12

2.3.5 PFC過電流保護

PFC過電流保護は、図 10 のように PFC MOSFETの Source-GND間に接続された過電流検出抵抗

により決定される電圧を CSP端子で監視することで行います。

CSP端子電圧が Vcsp 0.5V以上で PFCの主 SWを即オフします。通常動作時の最大ドレイン電流以

上、且つチョーク飽和電流以下で過電流検出ポイントを設定して下さい。

なお、本 ICにはゲートオン直後のノイズによる過電流保護の誤動作防止の為、ゲートオン信号が入って

から一定期間、過電流検出を受け付けないリーディングエッジブランク時間 TLEB 500nsを設けています。

内部フィルタ期間は、約 400nsです。

LLCや Standbyからのスイッチングノイズによる誤動作防止の為、図 10 のようにコンデンサを挿入して

下さい。コンデンサは、CSP-GND間直近に接続して下さい。CSP-GND間コンデンサは 0.1uF程度を推

奨いたします。また、抵抗 RCSP2を追加することによりさらにノイズによる誤動作防止を抑制できます。この

場合の抵抗値は、10Ω程度を推奨いたします。

CSP端子の設計方法は 3.4 項をご覧下さい。

内部フィルタ期間

TLEB

ID

CSP +0.5V

CSP

RCSP2

CCSP RCSP1

VGP

図 10 . PFC部 CSP端子接続例および動作シーケンス

2.3.6 フィードバック端子オープンショート保護

FBP端子が GNDに対してショート状態になった場合の保護として、FBP端子電圧は、Vfb(L) 0.4V以

下になると PFC部の発振を停止する機能を有しています。そのため、ショート状態になった場合でも安全

に停止します。

また FBP端子オープン時の保護として、IC内部の FBP端子-GND間に数 uA程度のプルダウン電流

源が内蔵されており、端子オープン時にこの端子は GND電位まで下がります。その為、FBP端子電圧が

Vfb(L) 0.4V 以下になり PFC部は発振停止するため、安全に停止します。

2.3.7 低入力電圧保護

本 IC では入力電圧を検出していない為、AC 入力電圧が低い場合でも FBP 端子電圧>0.4V であれば、

ICからゲート信号は出力され発振します。

しかし、その状態が続くと主 SWやその他のデバイスへの負担が大きくなる為、本 ICでは最大 ON時

間を設定し、オン幅の制限を行っております。

これにより、IC内部で設定された最大 ON時間 Ton(max) 27.5usでオン幅をクランプして出力を垂下

させる事が出来るので、低入力電圧でも主 SWやその他デバイスへの負担を軽減することが出来ます。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 12 -

Page13

2.3.8 軽負荷時 PFC出力電圧上昇防止機能

軽負荷時は、ゲートのオン幅を絞り込むことで出力を安定させます。しかし、最小オン幅まで絞り込んで

も出力電圧が上昇する場合には出力電圧上昇を抑える為、COMP端子電圧が Vth(burst) 0.8V以下で

ゲート発振停止するシーケンスを内蔵してあります。これにより、軽負荷時に必要以上の電力を出力側に

供給することなく、出力電圧上昇を抑える事が可能となります。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 13 -

Page14

2.4 LLC部

2.4.1 LLCゲートドライバ (VGL、VGH端子)

LLCのゲート出力は VGL、VGH端子より出力されます。

LLCゲートドライバ駆動能力は、0.18A(Source)/0.38A(Sink)です。この値は、信号系誤動作を引き起こ

さずに MOSFETを十分高速にドライブできるように設計されています。一般的に用いられる駆動回路の

例を図 11(A)に示します。図 11(B),(C)のように電荷引き抜き用ダイオードを用いる場合には小容量ショッ

トキーダイオードなどを用い、スナッピー(ハード)リカバリーダイオードは使わないように注意して下さい。

推奨ダイオード例として 新電元製 D1NS4(アキシャル)や M1FM3(面実装)があります。

A)

Qa

Qb

VG(L/H)

PGND / VS

B) C)

Qa Qa

VG(L/H)

Qb Qb

VG(L/H)

PGND / VS PGND / VS

図 11 . ゲート駆動回路例

2.4.2 LLC部発振制御部 (FBL端子)

MCZ5205SE の LLC 部出力である主 SW の VGL,VGH は FBL 端子に接続されたオシレーター(以下、

OSC)用コンデンサ Ctの充放電により決定されます。VGL,VGH出力は Ctの放電時にそれぞれ出力され、

VGL,VGH出力が交互に出力することで、主 SWが交互に ON/OFFします。また、Ctの充電時間は

VGL,VGH出力が同時に OFFするデッドタイム(以下、DT)になります(図 12参照)。

FBL

FBL

FB

VGH

Ct

Rt VGL

PC1

DT DT DT DT

図 12 . FBLおよび VGL、VGH動作波形

本 ICは周波数、ON duty変調タイプです。周波数は FBラインに接続された FB制限抵抗に流れる FB

電流により変動し、ON dutyは発振周波数に合わせて変動します(図 13参照)。軽負荷時など、周波数が

最大になる条件においてはデッドタイムが広くなるため全周波数範囲において ZVS(Zero Voltage

Switching)確保が容易です。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 14 -

Page15

最低発振周波数は FBL端子に接続された Ctコンデンサ容量と並列に接続している Rtの外付け抵抗

によって決定されます。最高発振周波数は、FBL端子に接続された Ctコンデンサ容量と並列に接続して

いる Rtおよび FB抵抗値によって決定されます。連続動作時最高発振周波数 fmax は 300kHz以下を

推奨いたします。また、ソフトスタート動作時の初期発振周波数 fssは Ctコンデンサ容量により変化します。

詳細は、電源特性仕様書の特性図をご覧下さい。

frequency vs du ty frequency vs deadt ime

50 800

Ct=1500pF Ct=1500pF

Ct=1200pF 700 Ct=1200pF

Ct=1000pF Ct=1000pF

45 600

Ct=820pF Ct=820pF

500

40 400

300

35 200

100

30 0

0 50 100 150 200 250 300 350 400 0 50 100 150 200 250 300 350 400

frequency [kHz] frequency [kHz]

図 13 . 発振周波数および Duty と FB制限抵抗特性

2.4.3 Vsenブラウンアウト保護 (Vsen端子)

Vsen 端子は PFC出力電圧を監視し、その値に応じてゲートドライブパルス出力の禁止、発振周波数

の制御を行います。この機能により Vc1が印加されたままでの入力 Vbulk投入時或いは入力電圧の瞬

低および瞬断時などにコンバータが共振はずれ動作に移行することを防ぎます。

各端子の電圧と各出力のタイミングは図 14 を参考にして下さい。

入力上昇に伴い、Vsen端子電圧が Vsen1(ss-reset) 3.55V に達すると、SST端子への充電を行い、

SST端子電圧が Vss(st) 0.6V以上の時に LLCはゲート出力を開始します。これにより、発振開始直後

は発振周波数が高い状態から起動を開始し、徐々に SST端子が充電すると共に発振周波数を低くしてい

きます。(SSTについては、2.4.4項をご覧下さい。)

入力低下時は、Vsen端子電圧が Vsen2(ss-reset) 3.25V以下になると、SST端子を放電します。

SST端子が放電されることにより徐々に発振周波数を高くし、SST端子電圧が Vss(sp) 0.5V以下になる

と、ゲート出力は停止します。これにより、再度 Vsen端子電圧が Vsen1(ss-reset)以上になったときに発

振周波数が低い状態から発振し共振はずれになることを防ぎます。

また、Vsen SS-Resetしきい値にはヒステリシスがあるため、PFC出力電圧リップル等による Vsen

ON/OFF誤動作を防ぐことが出来ます。

なお、Vsen端子 ON/OFFのしきい値は、後述するアクティブスタンバイモード状態の有無によって自動

的に変わります。

・ 通常動作時(AS OFF) : Vsen ON 3.55V / Vsen OFF 3.25V

・ アクティブスタンバイモード時(AS ON) : Vsen ON 1.0V / Vsen OFF 0.9V

3.55V

Vsen 3.25V 1.0V

0.9V

Vc1

12.6V

SST

0.6V 0.6V

0.5V 0.5V

FBL

VGH

VGL

COMP

AS

図 14 . Vsen端子と各出力タイミングチャート図

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 15 -

du ty [% ]

dead t ime [n s]

Page16

2.4.4 ソフトスタート機能 (SST端子)

LLC部はソフトスタート機能を内蔵しており、SST端子-GND間に接続されたコンデンサを充電していく

ことにより発振周波数を徐々に広げて行きます。SST端子が充電される条件としては、以下の 2つを満た

している必要があります。

① Vc1端子電圧が、Vc1(start) 12.6V以上であること。

② Vsen端子電圧が、Vsen1(ss-reset) or Vsen3(ss-reset) 以上であること。

SST端子 0.6V以上で発振開始、その後は Vss(open) 2.1Vで一定となります。また、ヒステリシスを

持ち SST端子 0.5V以下で発振停止いたします。

SST端子電圧と発振周波数の関係は、図 15をご覧下さい。なお、詳細なデータは電源特性仕様書の

特性図をご覧下さい。

また、SST端子は、異常状態時に主 SWや周辺回路への負荷を軽減する為にタイマ間欠ラッチ停止機

能を備えております。タイマ間欠ラッチ停止機能の詳細は、2.4.8項をご覧下さい。

VSST vs frequency

500

Ct=1500pF

450

Ct=1200pF

400 Ct=1000pF

350 Ct=820pF

300

250

200

150

100

50

0

0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2 2.2

VSST [V]

図 15 . SST電圧と発振周波数の関係

2.4.5 過電流保護 (CSL端子)

LLC部の過電流保護(OCP)動作はパルスバイパルスで上下 MOEFETのドレイン電流を検出して動作

させます。CSL端子の OCP検出電圧は OCP(+/-) +/-0.350Vです。この検出電圧は十分に低く、電流検

出抵抗の無効な電力損失は抑制できます。

CSL端子電圧が OCP検出電圧に達すると、図 16のようにゲート出力は即オフされ FBL端子はその

時点で充電を開始して、同時に SST端子のコンデンサを充電します。(SST充電は 2.4.8項を参照下さ

い。) これにより、電流ピークをパルスバイパルスで抑制できます。

OCPを検出した次の周期(上側 MOSFETが OCP検出した場合、次の下側 MOSFET)の FBL端子放

電期間は 1.9Vまでに制限されます。これにより、OCP動作後の次の周期はオン幅が制限される為、オン

幅が伸びすぎて共振はずれに入ったり波形が暴れたりするのを防ぎます。

なお、電源設計上の注意点として、後述します 2.4.6項の di/dt保護機能により、通常動作における Ipk

よりも OCPレベルを著しく高く設計いたしますと、di/dt検出レベルも同時に高くなる為、通常電源動作時

に di/dt保護機能が働いて出力電圧が低下する場合があります。

また、本 ICでは MOSFETのスイッチングによって発生するノイズによる OCP誤動作防止のために、

図 16のように FBL端子放電開始から FBL端子電圧 Vfbl(msk) 2.8Vまでを OCPマスクしています。

よってこの期間は OCP検出しません。

また、ランダムに入るノイズによる誤動作防止のため CSL端子に内部フィルタを内蔵しています。この

フィルタの遅れにより、OCP検出~FBL急速充電開始まで約 200nsの遅れが生じます。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 16 -

frequency [kHz]

Page17

OCPマスク期間 内部フィルタ期間

FBL(Top)

マスク電圧

2.8V

1.9V

FBL(Bottom)

+0.35V

CSL 0V

-0.35V

VGH

VGL

図 16 . 過電流保護動作シーケンス

2.4.6 di/dt保護機能 (CSL端子)

MCZ5205SEは di/dt保護機能(共振はずれ検出)を搭載しています。di/dt保護機能はパルスバイパル

スで両方向の MOSFET ドレイン電流をモニタし、OCP保護動作同様に CSL端子で検出を行います。

di/dt検出電圧は Vdi/dt(+/-) +/-60mVです。(図 17を参照下さい。)

上側 MOSFET動作期間では OCPマスク期間後に CSL端子電圧が+60mVを下回るネガティブエッ

ジを検出してゲート出力は即オフされ FBL端子はその時点で充電を開始します。

下側 MOSFET動作期間では OCPマスク期間後に CSL端子電圧が-60mVを上回るポジティブエッジ

を検出してゲート出力は即オフされ FBL端子はその時点で充電を開始します。

また、スイッチングによって発生するノイズによる di/dt誤動作防止のために、FBL放電開始から FBL

端子電圧 Vfbl(msk) 2.8Vまで di/dt保護機能をマスクしています。よって、この期間に上記+/-60mVを横

切った場合、di/dt検出しません。

なお、アクティブスタンバイ ON/OFFにより、di/dt動作時の SST端子充電シーケンスが異なります。

・通常動作時(AS OFF) : di/dt動作で SST端子のタイマ充電は行いません。

・アクティブスタンバイモード時(AS ON) : di/dt動作で SST端子のタイマ充電を行います。

di/dtマスク期間 内部フィルタ期間

FBL(Top)

マスク電圧

2.8V

FBL(Bottom)

+0.06V

CSL 0V

-0.06V

VGH

VGL

図 17 . 共振はずれ保護動作シーケンス

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 17 -

Page18

2.4.7 起動時 di/dt保護機能 (Tss(3)機能)

LLC電流共振回路の電源動作開始直後、共振コンデンサの電圧が不安定な過渡的状態において、

MOSFET に流れる電流がボディダイオードに流れている期間中にゲートがオフしてしまう場合があります。

この状態では、ボディダイオードの trr成分により、反対側 MOSFETがオンした際に短絡電流が流れてし

まい MOSFETに負荷がかかります。

本 ICでは Tss(3)機能を内蔵しており、この起動時のボディダイオード導通中にゲートがオフすることを

回避できます。Tss(3)シーケンスは図 18のように電源動作開始後 2発目のローサイド側 VGL出力時に

FBL端子の Ct充電開始電圧値を 0.8Vまで下げることでローサイドのオン幅を伸ばします。これにより、

MOSFETが正方向に電流が流れてからゲート出力をオフすることが出来ます。

FBL(Top)

FBL(Bottom)

0.8V

VGH

VGL

IDH

IDL

図 18 . Tss(3)動作シーケンス

2.4.8 タイマ間欠ラッチ停止機能 (SST端子)

SST端子コンデンサ Csstは以下の条件の時に充電を開始します。

① OCP動作時

② アクティブスタンバイモードでの di/dt保護動作時

上記状態が続き、異常信号が入り続けて SST端子電圧が Vtimer(set) 3.6Vまで達しますと間欠動作

モードになります。間欠動作モード中に異常信号が無くなると正常発振に戻りますが、この間欠発振モード

が連続で 2回カウントされると ICがラッチ停止します。ラッチリセットは Vc1<8.1Vです。

OCP動作やアクティブスタンバイモード時の di/dt保護動作が働くと、SST端子は FBL端子の充放電

8周期間分 SST端子の充電を行います。SST端子充電電流 Itimer(charge)は 40μAです。

詳細は図 19 をご覧下さい。

また、図 19のようにラッチカウンタのリセット機能を搭載しています。ラッチカウンタリセット条件は以下

の2つです。

① SST = 2.1V到達時

② SSリフレッシュ時 (Vc1 ON/OFF時)

この機能により、電源が正常に機能するとラッチカウンタは 0になります。異常状態が継続された場合

は、ラッチカウンタリセットを行わず、2回カウント後はタイマーラッチ停止になります。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 18 -

Page19

Vc1 Vc1(stop) Vc1(start)

8.5V 12.6V

負荷短絡 状態

短時間の過負荷

LLC ID

OCP動作

異常検出信号 OCP動作 OCP動作

(IC内部)

Vtimer1 3.6V

2.1V 1.5V

SST

0.6V Vtimer2 0.35V

図 19 . SST動作シーケンス

2.4.9 ハイサイドドライバ電源

ハイサイド MOSFET駆動用フローティング電源(VB)は、図 20に示すように Vc2端子の 10.2Vレギュ

レータ出力コンデンサを電圧源として高圧側へ向かうダイオード Dbootとフローティング平滑コンデンサ

Cbootによるブートストラップ回路により生成されます。

外付け Dbootによるブートストラップ回路採用によりローサイドとハイサイドの電位差が最小限に保た

れ、過渡的にも安定した駆動用電源が供給できます。

Cbootには MLCCを用い、その値は 0.1uF-1.0uFを推奨します。また Dbootには高速かつソフトリカ

バリー特性を持った 600V耐圧以上のものを用いて下さい。新電元製 D1NK60或いは D1FK60(面実

装)を推奨いたします。(PFC出力電圧を約 400Vとした場合。)

Np

Cboot

0.1 uF

16V Dboot

D1NK60

D1FK60

VGH VS VB VGL PGND Vc2

MCZ5205SE

図 20 . Boot Strap ハイサイド Vcc生成回路

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 19 -

Page20

2.5 共通部

2.5.1 アクティブスタンバイ機能 (AS端子)

本 ICは、アクティブスタンバイ機能を備えており、軽負荷時の損失低減に貢献します。アクティブスタン

バイ回路構成例は、図 21をご覧下さい。

AS端子は、AS端子電圧が Vas(on) 0.8V以下でアクティブスタンバイモードへ移行します。アクティブ

スタンバイモード移行後、AS端子電圧を Vas(off) 1.0V以上にすることでアクティブスタンバイモードから

通常動作モードへ移行します。

AS端子には、ノイズによる誤動作防止のために IC直近にコンデンサを挿入して下さい。フィルタ用コ

ンデンサは、1000-10000pF 程度を推奨いたします。(AS機能を使用しない時も誤動作防止の為、1000-

10000pF程度のフィルタ用コンデンサを挿入して下さい。)

AS端子は、端子オープン時に Vas(open) 2.4Vになるように調整されております。アクティブスタンバイ

回路構成例(図 21)のように、フォトカプラを ONさせて AS端子をショートするとアクティブスタンバイモード

に移行します。

AS

latch

4.5V.ref

2.4V.ref

AS

AS信号

AS

mode

1.0V/0.8V 10000pF

50kΩ

図 21 . アクティブスタンバイ回路構成例

アクティブスタンバイモードに入ると、以下の動作を行います。(図 22をご参照下さい。)

① LLC部動作モードを対称動作から非対称動作へ切り替える。

② Vsenしきい値(SS-Reset)を、3.55V/3.25Vから 1.0V/0.9Vへ切り替える。

③ di/dt動作時の SST端子充電を有効に切り替える。

④ PFC部の発振を停止する。

LLC部を非対称動作に切り替えることにより、軽負荷時の励磁電流ピークが抑えられるため、損失低減

が期待できます。また、PFCの発振を停止するシーケンスを内蔵しているため、PFC部損失を抑えること

ができます。これにより、軽負荷領域での大幅な効率改善が期待できます。

また、PFCが発振を停止して PFC出力電圧が下がった状態でも安全に動作できるように、自動で

Vsenしきい値(SS-Reset)を切り替えます。このシーケンスは、IC内部で行いますので追加周辺部品は不

要です。これにより、アクティブスタンバイモード時も低入力保護が働きます。

さらにアクティブスタンバイモード時は di/dt動作時の SST端子タイマ充電を有効にし、過電流保護を行

っています。

アクティブスタンバイのオン/オフ時のシーケンスにつきましては、図 22をご覧下さい。

SHINDENGEN

ELECTRIC MFG.CO.,LTD

- 20 -